The RZ/V series is a microprocessor (MPU) that incorporates Renesas' proprietary AI accelerator, Dynamically Reconfigurable Processor (DRP)-AI, which combines high AI inference performance and low power consumption. With a wide range of scalability from 0.5 to 80TOPS, RZ/V provides high added value for your various AI applications.

AI Accelerator: DRP-AI

DRP-AI is Renesas' dedicated hardware that provides high performance and low power consumption, and the ability to respond to evolution.

OpenCV Accelerator

OpenCV Accelerator leverages Renesas' unique, highly flexible DRP technology.

Partner Solutions

Partner products and services that support the RZ/V series can speed up your design and get to market faster.

RZ/V AI Apps & AI SDK

Jumpstart AI application development by using AI SDK samples of RZ/V2H, RZ/V2L or RZ/V2N with its respective evaluation boards.

DRP-AI TVM

Convert AI models from AI frameworks (ONNX/Pytorch/Tensorflow) into object code for DRP-AI processing.

Target Applications

- IP camera

- Surveillance camera

- Retail

- Logistics

- Image inspection

- Vision AI Gateway

Featured Products

| Product | Description | Featured Document |

|---|---|---|

| RZ/V2H | Quad-core Vision AI MPU with DRP-AI3 Accelerator and High-Performance Real-time Processor | |

| RZ/V2L | General-purpose microprocessor with Renesas' proprietary DRP-AI AI accelerator, a 1.2GHz dual-core Arm® Cortex®-A55 CPU, and a 3D graphics and video codec engine | |

| RZ/V2N | 15TOPS Quad-Core Vision AI MPU with 2-Camera Connection and Excellent Power Efficiency |

Specification Summary

| RZ/V2H | RZ/V2N | RZ/V2L | RZ/V2M | RZ/V2MA | |

|---|---|---|---|---|---|

| Main CPU | Arm® Cortex®-A55 (1.8GHz) Quad | Arm Cortex-A55 (1.8GHz) Quad | Arm Cortex-A55 (1.2GHz) Dual/Single | Arm Cortex-A53 (1.0GHz) Dual | Arm Cortex-A53 (1.0GHz) Dual |

| Sub CPU | Arm Cortex-R8 (800MHz) Dual Arm Cortex-M33 (200MHz) Single | Arm Cortex-M33 (200MHz) Single | Arm Cortex-M33 (200MHz) Single | --- | --- |

| AI Accelerator | DRP-AI3 | DRP-AI3 | DRP-AI | DRP-AI | DRP-AI |

| Image Processing Accelerator | DRP | --- (*1) | --- (*1) | --- | DRP |

| DRAM-I/F | 2 x LPDDR4/4X-3200 32-bit | LPDDR4/4X-3200 32-bit | DDR3L-1333/DDR4-1600 16-bit | LPDDR4-3200 32-bit | LPDDR4-3200 32-bit |

| ISP | Arm Mali™-C55 ISP | Arm Mali-C55 ISP | --- (*2) | 4K/30fps, HDR/3DNR, etc. | --- |

| Video Codec | H.264/265 Enc/Dec (4K/30fps) | H.264/265 Enc/Dec (4K/30fps) | H.264 Enc/Dec (2K/30fps) | H.264/265 Enc/Dec (4K/30fps) | H.264/265 Enc/Dec (4K/30fps) |

| Graphics Engine | Arm Mali-G31 3D GPU | Arm Mali-G31 3D GPU | Arm Mali-G31 3D GPU | 2D GPU | --- |

| Camera-I/F | 4x MIPI® CSI-2® (4-lane) | 2x MIPI CSI-2 (4-lane) | 1x MIPI CSI-2 (4-lane) 1x Parallel | 2x MIPI CSI-2 (4-lane) | --- |

| Display-I/F | 1x MIPI DSI® (4-lane) | 1x MIPI DSI (4-lane) | 1x MIPI DSI (4-lane) 1x Parallel | HDMI 1.4a | --- |

| Peripherals | 2x USB 3.2 (Gen2), 2x USB2.0, 2x GbEther, 6x CAN-FD, 1x PCIe® (Gen3) | 1x USB 3.2 (Gen2), 1x USB2.0, 2x GbEther, 6x CAN-FD, 1x PCIe (Gen3) | 2x USB2.0, 2x GbEther, 2x CAN-FD | 1x USB3.1, 1x GbEther, 1x PCIe Gen2 | 1x USB3.1, 1x GbEther, 1x PCIe Gen2 |

| Package | 1368-pin FCBGA (19mm x 19mm, 0.5mm pitch) | 840-pin FCBGA (15x15mm, 0.5mm pitch) | 456-pin LFBGA (15x15mm, 0.5mm pitch) 551-pin LFBGA (21x21mm, 0.8mm pitch) | 841-pin FCBGA (15x15mm, 0.5mm pitch) | 841-pin FCBGA (15x15mm, 0.5mm pitch) |

(*1) OpenCV Accelerator function provided as DRP library; Exclusive use with DRP-AI

(*2) Simple ISP function provided as DRP library; Exclusive use with DRP-AI

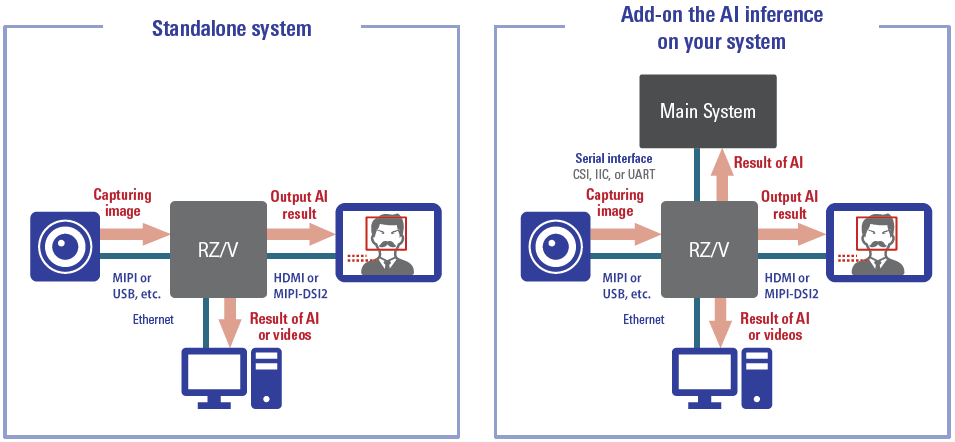

Use Case

Software & Tools

| Software title | Software type | Company |

|---|---|---|

| DRP-AI Translator [V1.90] This is an AI model conversion tool (DRP-AI Translator) for DRP-AI equipped products. This product is also used as an internal tool for DRP-AI TVM (required when installing DRP-AI TVM). | Software Package | Renesas |

| DRP-AI TVM (GitHub) We provide an AI model conversion tool (DRP-AI TVM) for DRP-AI-equipped products. When using this product, please check the contents of the linked README.md first. | Software Package | Renesas |

| RZ/V series AI Apps & AI SDK (GitHub) The AI SDK enables easy and rapid development of AI applications using Renesas' RZ/V series evaluation kits. Additionally, it offers a range of AI applications free of charge. | Software Package | Renesas |

3 items | ||

Videos

The RZ/V2N is a vision AI microprocessor (MPU) featuring Renesas' proprietary AI accelerator (DRP-AI3), delivering up to 15TOPS AI performance with high power efficiency in a compact design. Its ability to support two-camera connections greatly improves AI accuracy and can simultaneously process different captured images with AI, making it ideal for AI camera and robotics applications.