Features

- CPU: Arm Quad Cortex-A55, maximum operating frequency 1200MHz

- CPU: Arm Dual Cortex-R52, maximum operating frequency 1000MHz

- Memory: Tightly coupled memory 576KB (with ECC) per R52 core, internal RAM 2MB (with ECC)

- LPDDR4 SDRAM memory interface

- Trigonometric function accelerator

- 3-port Gigabit Ethernet switch with TSN and 3-unit Ethernet GMAC

- Industrial Ethernet: EtherCAT®, PROFINET® RT/IRT, EtherNet/IP™, etc.

- Encoder interface: 16ch (supports A-format™, EnDat, BiSS®, HIPERFACE® DSL, FA-CODER)

- Up to 9-axis motor control

- Octa/Quad SPI support

- ADC: 12-bit 4ch x 2 units + 6ch x 1 unit

- ΔΣ I/F: 30ch

- Package: 729-pin FCBGA

- Voltage: 0.8V core, 1.1V DDR 1.8V PLL, OSC, USB I/O 3.3V GPIO, xSPI, RMII, MII

Description

RZ/T2H is an advanced high-end microprocessor (MPU) providing high application processing performance, high-precision real-time control, and Linux operations on a single chip. It has the processing power and peripheral functions required for controllers such as industrial robots, motion controllers, and programmable logic controllers (PLCs). Quad Arm® Cortex®-A55 CPU cores (1200MHz) for application processing and two Arm Cortex-R52 CPU cores (1000MHz) for real-time control, as well as network functions compatible with Time-Sensitive Networking (TSN) and various industrial Ethernet protocols such as EtherCAT, EtherNet/IP, and PROFINET RT/IRT. The peripheral functions are capable of controlling motors of up to 9 axes with low latency access from a Cortex-R52 CPU. Equipped with a large-capacity memory interface of LPDDR4, and a large-capacity non-volatile memory interface of SD/eMMC, it supports application-rich operating systems such as Linux. Two lanes of PCIe Gen3, 2 channels of xSPI, and other high-speed interfaces are also available. Multi-axis motor control can be achieved with a single chip, reducing the number of BOM components, thus contributing to reduced power consumption and board size.

Parameters

| Attributes | Value |

|---|---|

| CPU Architecture | Arm |

| Main CPU | Cortex-A55, Cortex-A55 x 2, Cortex-A55 x 4 |

| Program Memory (KB) | 0 |

| RAM (KB) | 3200 |

| Carrier Type | Bulk (Tray), Full Carton (Tray) |

| Supply Voltage (V) | - |

| I/O Ports | 287 |

| NPU | No |

| DRAM I/F | LPDDR4-3200 |

| 3D GPU | No |

| Temp. Range (°C) | Tj = -40 to +125 |

| Operating Freq (Max) (MHz) | 1200 |

| Ethernet speed | 10M/100M/1G |

| Ethernet (ch) | 4 |

| EtherCat (ch) (#) | 1 |

| USB FS (host ch/device ch) | ( 1 / 1 ) |

| USB HS (host ch/device ch) | ( 1 / 1 ) |

| USB SS (host ch/device ch) | ( 0 / 0 ) |

| PCI Express (generation and ch) | PCIe (Gen3.0 2Lane) x 1 ch |

| SCI or UART (ch) | 18 |

| SPI (ch) | 4 |

| I2C (#) | 3 |

| CAN (ch) | 0 |

| CAN-FD (ch) | 2 |

| Wireless | No |

| SDHI (ch) | 2 |

| High Resolution Output Timer | No |

| PWM Output (pin#) | 63 |

| 32-Bit Timer (ch) | 59 |

| 16-Bit Timer (ch) (#) | 14 |

| 8-Bit Timer (ch) | 0 |

| Standby operable timer | No |

| Asynchronous General Purpose Timer / Interval Timer (ch) | 0 |

| 16-Bit A/D Converter (ch) | 0 |

| 14-Bit A/D Converter (ch) | 0 |

| 12-Bit A/D Converter (ch) | 14 |

| 10-Bit A/D Converter (ch) | 0 |

| 24-Bit Sigma-Delta A/D Converter (ch) | 0 |

| 16-Bit D/A Converter (ch) | 0 |

| 12-Bit D/A Converter (ch) | 0 |

| 10-Bit D/A Converter (ch) (#) | 0 |

| 8-Bit D/A Converter (ch) | 0 |

| Capacitive Touch Sensing Unit (ch) | 0 |

| Graphics LCD Controller | Yes |

| MIPI Interfaces (DSI) (ch) | 0 |

| MIPI Interfaces (CSI) (ch) | 0 |

| Image Codec | No |

| Segment LCD Controller | No |

| Security & Encryption | AES, RSA, ECC, Hash, TRNG, Arm TrustZone, Secure boot, Unique ID, Arm TrustZone, Unique ID |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| FCBGA | 23 x 23 x 2.4 | 729 | 0.8 |

Application Block Diagrams

|

9-Axis Industrial Motor Control with Ethernet

High-precision and efficient 9-axis motor control designed for robotics and industrial applications.

|

Additional Applications

- Industrial robot (articulated robot, parallel link, SCARA robot)

- Collaborative robot

- AGV/AMR

- Multi-axis servo

- CNC

- Motion controller

- PLC

Applied Filters:

Filters

Software & Tools

Sample Code

Simulation Models

e² studio (Renesas)

If you would like to use e² studio, download "e² studio and RZ/T2 FSP Installer" from Software Downloads below.

IAR Embedded Workbench for Arm (IAR Systems)

If you would like to use IAR Embedded Workbench for Arm as the integrated development environment, please contact IAR. Also, please download and use together with "RZ/T2 FSP Smart Configurator and FSP Installer (for IAR Embedded Workbench)" and "EWARM Patch File for RZ/T2H and RZ/N2H" from Software Downloads below.

Flexible Software Package (FSP)

Software package for developing embedded systems using RZ/T2H. Installer in Software Downloads includes latest version of FSP.

This video explains sample program setup procedures for EtherCAT® salve functionalities with the adapted EtherCAT Stack Code for the Renesas RZ/T2H platform. It covers the steps to verify slave behavior and stack features with the TwinCAT® Master Configuration tool.

Chapter's Title

00:10 Overview

01:14 Board Setting

03:35 Generating the Slave Stack Code

04:25 Setting Up TwinCAT3

07:08 Run the Demonstration

Related Resources

This video provides a complete walkthrough for setting up the RZ/T2H and RZ/N2H evaluation boards using the Linux Board Support Package (BSP). It covers everything from build procedures, board setup, and boot loader configuration to Software Development Kit (SDK) creation. The video also demonstrates running a sample program that combines Linux and real-time control using the Flexible Software Package (FSP), where Linux prints "Hello World!" while FSP on e² studio controls a blinking LED.

Chapter Titles

00:31 Environmental Requirements

01:24 Setting Up Environment

03:46 Boot Implementation

07:53 Example Implementation of Linux and FSP

Related Resources

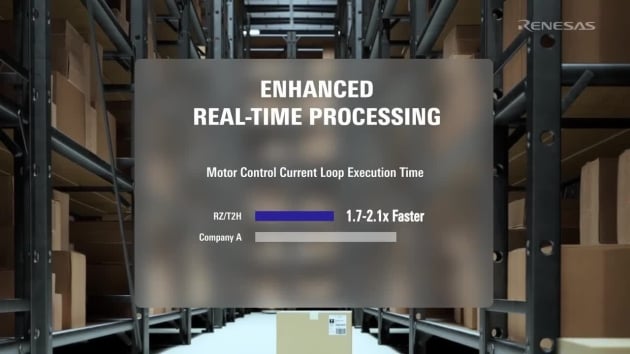

This video provides an overview of the RZ/T2H MPU, featuring enhanced real-time capabilities, fast application processing, and multi-axis control for industrial automation.

This video demonstrates the RZ/T2H's capability to control up to nine motor axes. It covers the demo's structure, highlights its key features, and showcases multi-axis control using the motion control utility. To learn more, visit the RZ/T2H evaluation board.

Related Resources

This video delves into OpenAMP, showcasing its role in managing inter-processor communication within a single device. Learn how OpenAMP effectively facilitates communication between the multiple cores of the RZ/T2H, enhancing the device's performance. Visit the RZ/T2H page to learn more.

This video provides an overview of all the tabs in the FSP Configuration, except for the [Pin] tab, which is covered in the Pin Configuration Function video.

Chapter's Title

00:10 Overview

00:44 Introduction of Summary Tab

01:22 Introduction of Bsp Tab

03:39 Introduction of Clocks Tab

04:52 Introduction of Stacks Tab

05:42 Introduction of Interrupts Tab

06:30 Introduction of Event Links Tab

07:13 Introduction of Components Tab

Related Resources

FSP Links

Board Links

User's Manual links

Video Link

This video guides you on how to use commonly used tabs in FSP configuration. Tabs excluded include the [Pin] tab, which is covered in the Pin Configuration Function video. The [Summary] tab and [Components] tab are rarely used.

Chapter's Title

00:00 Overview

01:08 BSP Tab in FSP Configuration

03:51 Clocks Tab in FSP Configuration

04:47 Stacks Tab in FSP Configuration

06:09 Example of Stacks Configuration

10:20 Interrupts Tab in FSP Configuration

13:10 Event Links Tab in FSP Configuration

Related Resources

FSP Links

Board Links

User's Manual Links

Video Link

This video shows you how to use the FSP - Pin Configuration function for RZ/T and RZ/N devices. It teaches you how to set up pins using the Pins tab and shows examples of pin conflicts. It also shows what the pin setup looks like when it’s done, so you can check your work.

00:29 Introduction of Pin Configuration

04:36 Features Available in Pin Configuration GUI

07:28 Pin Conflict Example

11:57 Pin Configuration Output and Usage

FSP links

Board links

This training video will show you how to install the development tools that will enable you to start developing applications using e2 studio for the Renesas RZ/T and RZ/N series of MPUs.

There are settings specific to each product and version. Refer to the document below for details.

RZ/T2,RZ/N2 Getting Started with Flexible Software Package

(PDF)

FSP links

Board links

00:36 STEP 1 Installation of e2 studio and FSP

03:19 STEP 2 Create a New Project

05:11 STEP 3 Run the Project

This training video will show you how to install the development tools that will enable you to start developing applications using IAR Embedded Workbench for ARM (EWARM) for the Renesas RZ/T and RZ/N series of MPUs.

There are settings specific to each product and version. Refer to the document below for details.

RZ/T2,RZ/N2 Getting Started with Flexible Software Package

(PDF)

FSP links

Board links

00:37 STEP 1 Installation of EWARM and FSP SC

01:48 STEP 2 Create a New Project

03:51 STEP 3 Run the Project

This video provides an overview of 9-axis motor control using the RZ/T2H MPU. The demonstration features a single RZ/T2H device operating as both an EtherCAT Controller and Sub Device while executing precise 9-axis motor control.

Chapter Titles

0:11 Overview

0:26 RZ/T2H Overview

1:09 RZ/T2H 9-axis Motor Control Demo Configuration

2:37RZ/T2H Software Configuration

4:06 RZ/T2H 9-axis Motor Control Demo

Related Resources