特長

- ロジック&ミックスド・シグナル回路

- 汎用性の高いマクロセル

- リードバック保護(リードロック)

- VDD 1.8V(±5%)~5V(±10%)

- 1.8V(±5%)~5V(±10%)VDD2(VDD2 ≤ VDD)

- 動作温度範囲:-40°C~85°C

- RoHS指令準拠/ハロゲンフリー

- マクロセル概要

- アナログコンパレータ(ACMP)x 4

- 2つの基準電圧(Vref)

- 19種類の組み合わせ機能マクロセル:

- 3つのDFF/ラッチまたは2ビットLUTを選択可能

- 連続DFF/ラッチまたは3ビットLUTのいずれかを選択可能

- 4つのDFF/ラッチまたは3ビットLUTを選択可能

- パイプ遅延または3ビットLUTのいずれかを選択可能

- プログラマブル関数発生器または2ビットLUTのいずれかを選択可能

- 5つの8ビット遅延/カウンタまたは3ビットLUTを搭載

- 2つの16ビット遅延/カウンタまたは4ビットLUTを搭載

- エッジ検出器を用いたデグリッチフィルタ x 2

- ステートマシン:

- 8つの状態

- 状態遷移からの柔軟な入力ロジック

- シリアル通信:

- I2Cプロトコル準拠

- パイプ遅延 – 16段/3出力(組み合わせ機能の一部)

- プログラマブルディレイ

- インバータ

- オシレータ(OSC)x 2:

- 25kHz/2MHzを設定可能

- 25MHzのRCオシレータ

- 水晶オシレータ

- パワーオンリセット(POR)

- 8バイトRAM+OTPユーザメモリ:

- RAM I2C経由で読み書き可能なメモリ空間

- OTPから転送されたユーザ定義の初期値

説明

SLG46538は一般的に使用される混合信号機能向けに、小型で低消費電力の部品を提供します。 ユーザーは1回限りの不揮発性メモリ(NVM)をプログラミングすることで回路設計を行い、SLG46538のインターコネクトロジック、I/O ピン、マクロセルを設定することができます。 この汎用性の高いデバイスにより、様々な混合信号機能を非常に小さく、低消費電力の単一集積回路内で設計することができます。 SLG46538の追加電源(VDD2)により、同一デザイン内で2つの独立した電圧領域のインタフェースを実現することができます。 VDDとVDD2の両方の電圧ドメインに対して、各電源専用のピンを入力、出力、またはその両方(内部ロジックで動的に制御)として構成することが可能です。 マクロセルを使用することで、両ドメインにまたがる混合信号機能の実装や、高→低、低→高の両方向のレベル変換のパススルーが可能です。

この製品は、デュアル電源GreenPAK™と非同期ステートマシン搭載GreenPAK™の両方の製品ラインで利用可能です。

本デバイスは、ルネサス事業所でのプログラム書き込みが可能です。

カスタムプログラムユーティリティをお試しください。

カスタムプログラムユーティリティをお試しください。

パラメータ

| 属性 | 値 |

|---|---|

| Nominal VDD | 1.71 - 5.5 |

| VDD2 (V) | 1.71 - 5.5 |

| GPIOs (#) | 16, 17 |

| Special Features | ASM (8 states) |

| ACMP Channels (#) | 4 |

| CNT/DLY (Max) (#) | 7 |

| LUTs (Max) (#) | 17 |

| D Flip-flops (DFFs) (#) | 8 |

| Pipe Delay | 16-stage |

| # of Programable Delays (#) | 1 |

| Oscillator Type | Conf. OSC, RC OSC, Crystal OSC, Conf. OSC, Ring OSC, Crystal OSC |

| Temperature Sensor (ch) (#) | 1 |

| Interface | I2C |

| Memory Type | OTP |

| Temp. Range (°C) | -40 to +85°C |

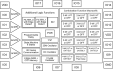

アプリケーション・ブロック図

| 低価格スマートインストルメントクラスタ 効率的なカスタムLCDに対応したバイクおよび車両ディスプレイ用のシングルチップ搭載の低価格スマートインストルメントクラスタ。 |

| レベル2 EV充電器 効率的なEV充電と管理のための高度な接続性を備えたモジュラEVSEシステム。 |

| 48V/3kW 2/3 輪車用モータ制御 48V/3kWのモータ制御システムは、スケーラブルなインバータ設計、位相過電流障害検出、ASIL-B安全性を特長としています。 |

| ロボット掃除機 このスマートロボット掃除機は、環境マッピング、落下防止、障害物検出、自動充電、アプリ制御を備えています。 |

| エントリークラスのHMIプラットフォーム エントリークラスのプラットフォームで、最新のHMIディスプレイ向けに信頼性の高い64ビット性能を提供します。 |

その他アプリケーション

- パソコン・サーバ

- PC周辺機器

- 民生機器全般

- データ通信機器

- モバイル用途/ポータブルエレクトロニクス