USB 2.0 ハイスピード/フルスピード対応 PHY

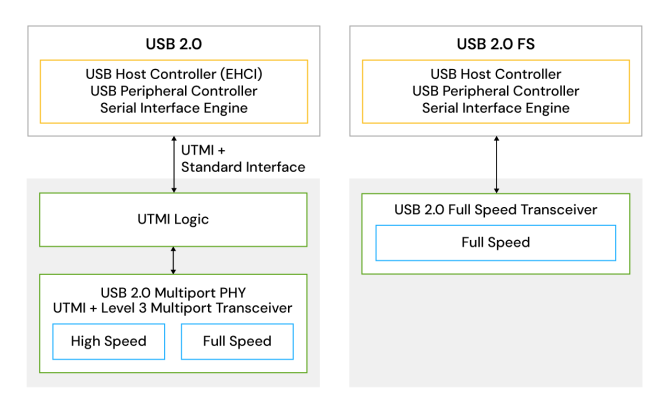

USB 2.0 PHYとUTMIロジックを組み合わせることで、標準インタフェース仕様(UTMI+ Level 3)に準拠したインタフェースソリューションを提供します。 さらに、USB 2.0 FSトランシーバは、USBフル/ロースピード用のI/OバッファをUSB 2.0 PHYから分離した構成で設計されており、より小さな面積でUSB 2.0 FSソリューションを実現します。

ルネサスのインタフェースIPは、PCIe/USB/SATA PHY、各種LINK IP、MIPI、FPD-Link、CAN、Ethernet AVB/TSNなどを含み、当社マイコン製品で豊富な採用実績を有しています。

以下のIPの一部は、設計利用契約済みです。 詳細は、当社までお問い合わせください。

| 基本機能 | IP名称 | プロセス(またはソフトマクロ) | 状況 | ドキュメント | 問い合わせ |

|---|---|---|---|---|---|

| USB LINK | USB 3.1 (Gen1) xHCI Host Controller | Soft macro | 準備中 (要問い合わせ) | 問合せ | |

| USB 3.1 (Gen1) Peripheral Controller | Soft macro | 準備中 (要問い合わせ) | |||

| USB 2.0 EHCI Host Controller | Soft macro | 量産中 | |||

| USB 2.0 Peripheral Controller | Soft macro | 量産中 | |||

| USB 2.0 OTG(On-The-Go)Controller | Soft macro | 量産中 | |||

| PCI Express LINK コンフィグレーションツール | Configurable PCI Express 4.0 Link Controller | Soft macro | 準備中 (要問い合わせ) | 問合せ | |

| PCI Express 5.0 Link Controller | Soft macro | 量産中 | |||

| CAN | CAN Controller | Soft macro | 準備中 (要問い合わせ) | 問合せ | |

| CAN FD | CAN FD Controller Multi-channel Type | Soft macro | 準備中 (要問い合わせ) | 問合せ | |

| CAN FD Controller Single-channel Type | Soft macro | 量産中 | |||

| Ethernet AVB | Ethernet AVB End Station | Soft macro | 準備中 (要問い合わせ) | 問合せ | |

| Ethernet TSN | Ethernet TSN End Station | Soft macro | 準備中 (要問い合わせ) | 適用例 | 問合せ |

| Ethernet TSN Layer 2/3 Switch | Soft macro | 準備中 (要問い合わせ) | 適用例 | ||

| FPD-Link | FPD-Link RX | TSMC 28nm | 量産中 | 問合せ | |

| FPD-Link RX | TSMC 22nm | 量産中 | |||

| FPD-Link TX | TSMC 28nm | 量産中 | |||

| FPD-Link TX | TSMC 22nm | 量産中 | |||

| LVDS | LVDS IO Buffer | TSMC 7, 12, 16, 22, 28, 40nm & Samsung 14nm | 量産中 | 問合せ | |

| PCIe/USB/SATA PHY | SerDes PHY up to 5Gbps PCIe2.1, USB 3.0 SS | TSMC 28nm | 量産中 | 問合せ | |

| USB2.0 PHY: Multi-Port Transceiver with UTMI+ Level 3 interface | TSMC 28nm | 量産中 | |||

| USB2.0 PHY: Multi-Port Transceiver with UTMI+ Level 3 interface | Samsung 28nm | 量産中 | |||

| USB2.0 PHY: Single-Port Transceiver with UTMI+ Level 3 interface | TSMC 40nm | 量産中 | |||

| USB2.0 PHY: Single-Port Transceiver with UTMI+ Level 3 interface | TSMC 22nm | 量産中 | |||

| USB 2.0 Full-Speed (FS) Transceiver | TSMC 22nm | 量産中 | |||

| MIPI D-PHY | MIPI D-PHY: Transmitter for DSI with FPD-Link TX | Soft macro&TSMC 22nm | 量産中 | 問合せ | |

| MIPI D-PHY: Receiver for CSI-2 | Soft macro&TSMC 22nm | 量産中 | |||

| MIPI D-PHY: Transceiver for CSI-2/DSI | Soft macro &TSMC 40nm | 量産中 | |||

| MIPI D-PHY: Transceiver for CSI-2/DSI | Soft macro&Samsung 28nm | 量産中 | |||

| MIPI D-PHY: Transceiver for CSI-2/DSI | Soft macro&TSMC 22nm | 量産中 | |||

| MIPI D-PHY(コントローラ) | MIPI CSI-2 Receiver IP Core | Soft macro | 準備中 (要問い合わせ) | 問合せ | |

| MIPI DSI-2 Transmitter IP Core | Soft macro | 準備中 (要問い合わせ) |

USB 2.0 PHYとUTMIロジックを組み合わせることで、標準インタフェース仕様(UTMI+ Level 3)に準拠したインタフェースソリューションを提供します。 さらに、USB 2.0 FSトランシーバは、USBフル/ロースピード用のI/OバッファをUSB 2.0 PHYから分離した構成で設計されており、より小さな面積でUSB 2.0 FSソリューションを実現します。

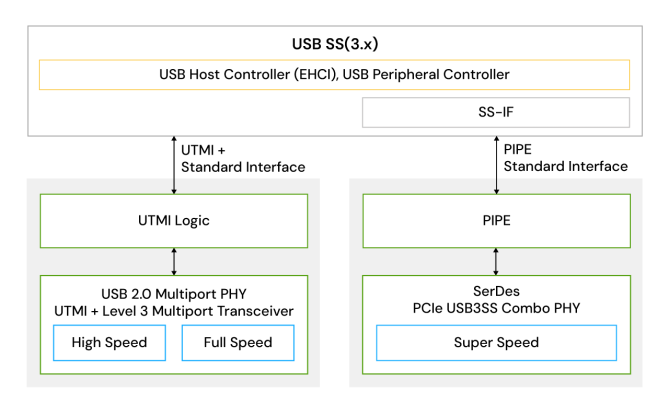

USB SuperSpeed用SerDes IP、PIPEロジック、USB 2.0 PHYおよびUTMIロジックを統合することで、標準インタフェース仕様(PIPE InterfaceおよびUTMI+ Level 3)に準拠したインタフェースソリューションを提供します。

SerDes IPとPIPEロジックを組み合わせることで、PCIe標準仕様に準拠したインタフェースソリューションを提供します。

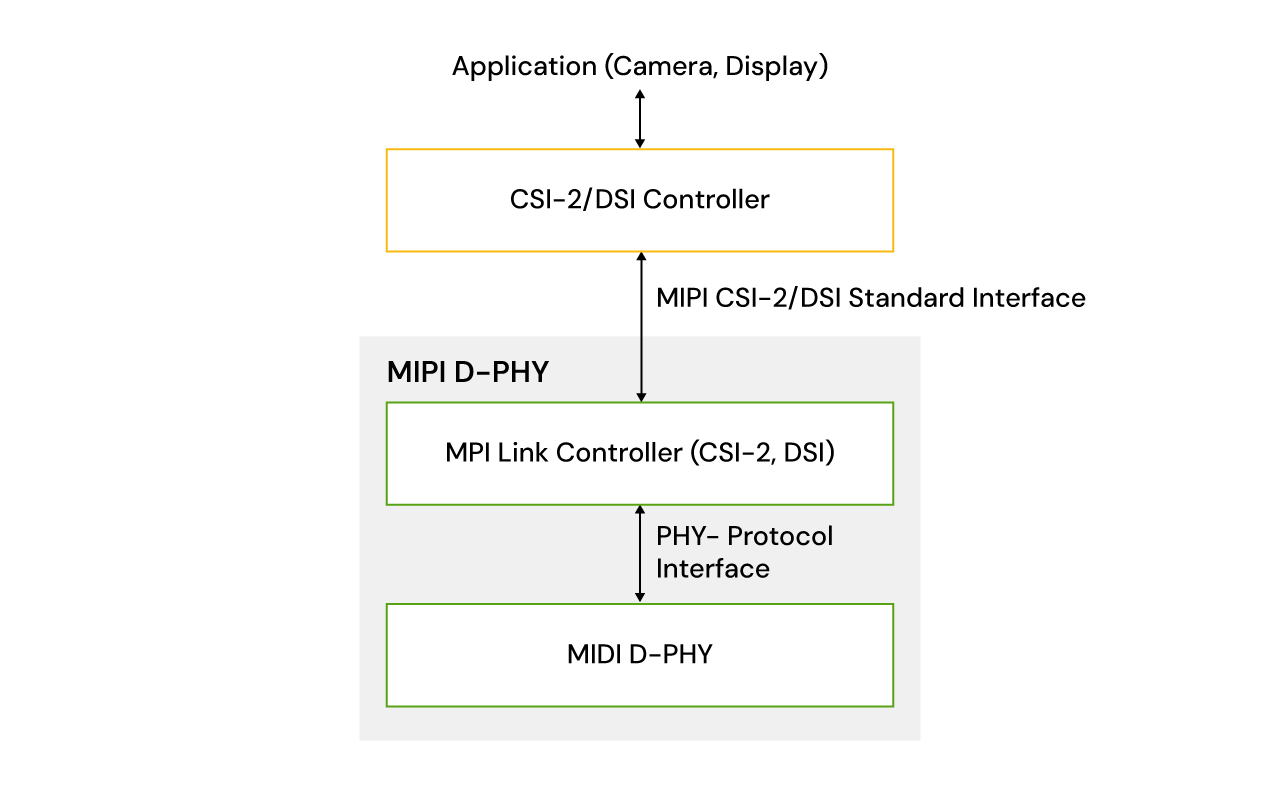

MIPI D-PHYは、高速シリアル通信向けに設計された物理層インタフェース規格であり、主にカメラ(CSI-2)およびディスプレイ(DSI)アプリケーションで使用されます。 CPU、グラフィックエンジン、システムメモリなどのコンポーネント間で、低消費電力かつ高帯域幅のデータ転送を可能にします。 MIPI CSI-2(カメラシリアルインタフェース2)およびDSI(ディスプレイシリアルインタフェース)に準拠したインタフェースソリューションは、MIPI D-PHY IPとMIPIコントローラIPによって提供可能です。