特長

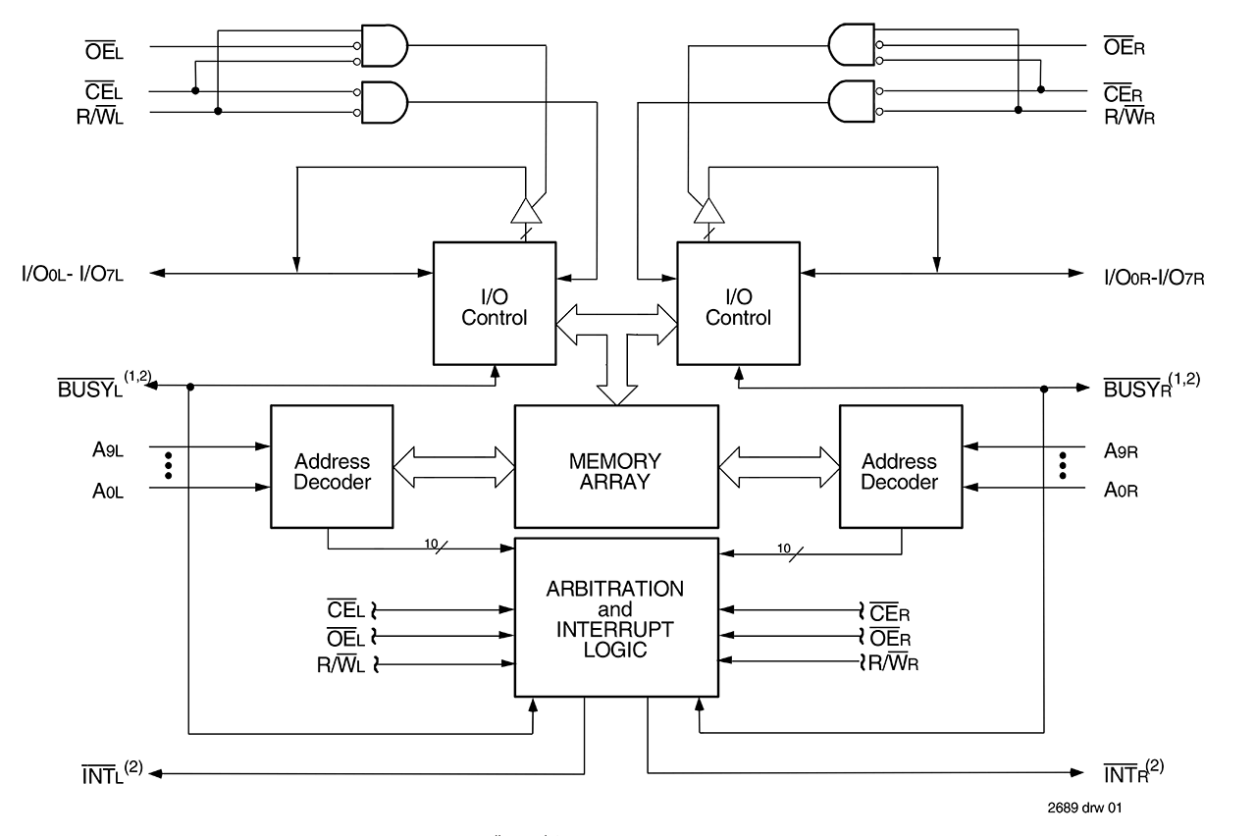

- True dual-ported memory cells allow simultaneous access of the same memory location

- On-chip port arbitration logic

- BUSY output flag

- INT flag for port-to-port communication

- Fully asynchronous operation from either port

- Battery backup operation – 2V data retention

- TTL-compatible, single 5V ±10% power supply

- Available in 48-pin Ceramic LCC, Flatpack, and 600-mil SDBRZ packages

説明

The 5962-86875 (7130/40) is a high-speed 1K x 8 dual-port static RAM designed to be used as a stand-alone 8-bit dual-port RAM or as a "Master" dual-port RAM together with a "Slave" dual-port in 16-bit or more word width systems, which would result in full-speed, error-free operation without the need for additional discrete logic. An automatic power-down feature, controlled by Chip Enable (CE) permits the on-chip circuitry of each port to enter a very low standby power mode. The military-grade product complies with MIL-PRF-38535 QML.

パラメータ

| 属性 | 値 |

|---|---|

| Core Voltage (V) | 5 |

| Bus Width (bits) | 8 |

| Density (Kb) | 8 |

| Pkg. Code | LC48 |

| Interface | Async |

| I/O Type | 5.0 V TTL |

| Access Time (ns) | 45 |

| Temp. Range (°C) | -55 to 125°C |

| Architecture | Dual-Port |

| Organization | 1K x 8 |

| Function | Busy, Interrupt, Master |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| LCC | 14.2 x 14.22 x 1.78 | 48 | 1.02 |

適用されたフィルター