特長

- ロジック&ミックスド・シグナル回路

- 汎用性の高いマクロセル

- リードバック保護(リードロック)

- VDD 1.8V(±5%)~5V(±10%)

- 1.8V(±5%)~5V(±10%)VDD2(VDD2 ≤ VDD)

- 動作温度範囲:-40°C~85°C

- RoHS指令準拠/ハロゲンフリー

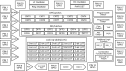

- マクロセル概要

- 8ビットSAR ADC(Successive Approximation Register Analog-to-Digital Converter:逐次近似型A/Dコンバータ)

- ADC 3ビットPGA(Programmable Gain Amplifier:プログラマブル利得アンプ)

- デジタル/アナログ・コンバータ(DAC)x 2

- アナログコンパレータ(ACMP)x 2

- 2つの基準電圧(Vref)

- 25のCombinatorial Look Up Tables(LUT):

- 2ビットLUT x 8搭載

- 3ビットLUT x 16搭載

- 4ビットLUT x 1搭載

- 1種類の組み合わせ機能マクロセル:

- パターンジェネレータまたは4ビットLUT

- デジタルコンパレータ/パルス幅変調器(DCMP/PWM)x 3、デッドバンド選択可能

- カウンタ/遅延(CNT/DLY)x 10:

- 14ビット遅延/カウンタ x 2

- 14ビット遅延/カウンタ(スリープ/ウェイク)x 1

- 14ビット遅延/カウンタ/有限状態機械 x 1

- 8ビット遅延/カウンタ x 5

- 8ビット遅延/カウンタ/有限状態機械 x 1

- Dフリップフロップ/ラッチ x 12

- パイプ遅延 x 2 - 16段/2出力、

- バンドギャップ x 2

- エッジ検出器付きプログラマブルディレイ x 2

- 内蔵オシレータ x 3

- 低周波

- リング

- RC 25kHzおよび2MHz

- パワーオンリセット(POR)

- スレーブSPI

説明

SLG46621は一般的に使用される混合信号機能向けに、小型で低消費電力の部品を提供します。 ユーザーは1回限りの不揮発性メモリ(NVM)をプログラミングすることで回路設計を行い、 SLG46621のインターコネクトロジック、I/O ピン、マクロセルを設定することができます。 この汎用性の高いデバイスにより、様々な混合信号機能を非常に小さく、低消費電力の単一集積回路内で設計することができます。 SLG46621の追加電源(VDD2)により、同一デザイン内で2つの独立した電圧領域のインタフェースを実現することができます。 VDDとVDD2の両方の電圧ドメインに対して、各電源専用のピンを入力、出力、またはその両方(内部ロジックで動的に制御)として構成することが可能です。 マクロセルを使用することで、両ドメインにまたがる混合信号機能の実装や、高→低、低→高の両方向のレベル変換のパススルーが可能です。

本デバイスは、ルネサス事業所でのプログラム書き込みが可能です。

カスタムプログラムユーティリティをお試しください。

カスタムプログラムユーティリティをお試しください。

パラメータ

| 属性 | 値 |

|---|---|

| Nominal VDD | 1.71 - 5.5 |

| VDD2 (V) | 1.71 - 5.5 |

| GPIOs (#) | 17 |

| Special Features | 2x DAC, 3x PWM, ADC (8-bit SAR) |

| ACMP Channels (#) | 6 |

| DCMP | 3 |

| CNT/DLY (Max) (#) | 10 |

| LUTs (Max) (#) | 26 |

| D Flip-flops (DFFs) (#) | 12 |

| Pipe Delay | 2x 16-stage |

| # of Programable Delays (#) | 2 |

| Oscillator Type | RC OSC, LF OSC, Ring OSC |

| Interface | SPI |

| Memory Type | OTP |

| Temp. Range (°C) | -40 to +85°C |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFN | 2.0 x 3.0 | 20 | 0.4 |

アプリケーション

- パソコン・サーバ

- PC周辺機器

- 民生機器全般

- データ通信機器

- モバイル用途/ポータブルエレクトロニクス