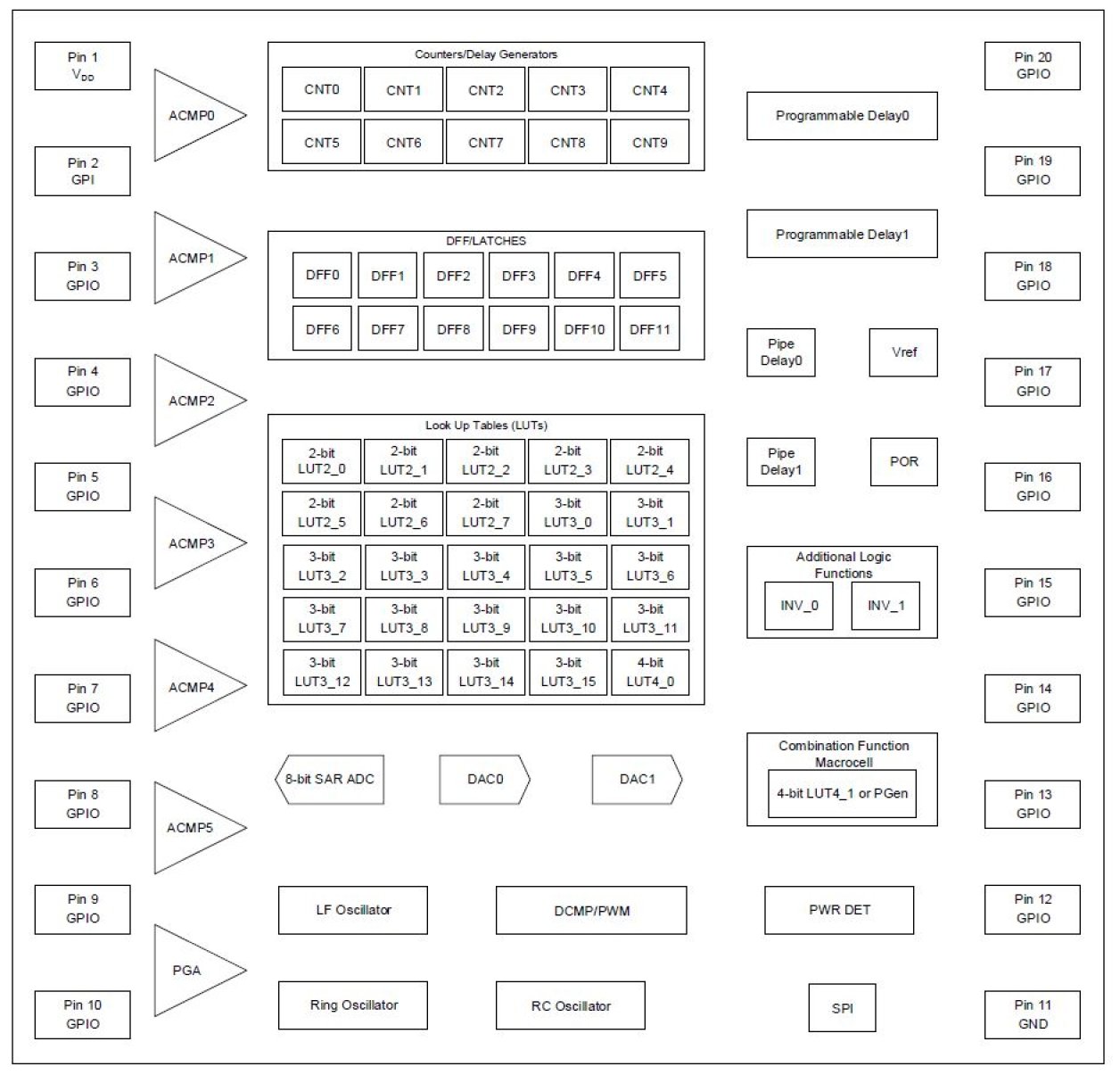

特長

- 8 ビット逐次比較型 A/D コンバータ (SAR ADC)

- ADC 3 ビット・プログラマブル・ゲイン・アンプ (PGA)

- 2つのD/Aコンバータ(DAC)

- 6つのアナログ・コンパレータ(ACMP)

- 2つの電圧リファレンス(Vref)

- 25 個の組み合わせルックアップ・テーブル (LUT)

- 8 つの 2 ビット LUT

- 16 個の 3 ビット LUT

- 1 4ビットLUT

- 1 組み合わせ関数マクロセル

- パターンジェネレータまたは4ビットLUT

- デッドバンドの選択が可能な3つのデジタル・コンパレータ/パルス幅変調器(DCMP/PWM)

- 10つのカウンタ/ディレイ(CNT/DLY)

- 2 つの14ビット遅延/カウンタ

- 1 つの 14 ビット遅延/カウンタ (WakeSleep 制御)

- 1 つの 14 ビット遅延/カウンタ/有限ステート マシン

- 5 つの8ビット遅延/カウンタ

- 1 つの 8 ビット遅延/カウンタ/有限ステート マシン

- 12つの D フリップフロップ/ラッチ

- 2 つのパイプ遅延 – 16 ステージ/2 出力

- エッジ検出機能付きの2つのプログラマブルな遅延

- 3つの内部発振器

- 低周波

- リング

- RC 25kHzおよび2MHz

- パワーオンリセット(POR)

- バンド ギャップ

- スレーブSPI

- 読み出し保護 (読み取りロック)

- 電源

- 1.8V(±5%)から5V

- 周囲動作温度範囲:40°C〜105°C

- RoHS対応/ハロゲンフリー

- パッケージ:20ピンSTQFN、2mm x 3mm x 0.55mm、0.4mmピッチ

説明

SLG46620-EVは、一般的に使用されるミックスド・シグナル機能用の小型で低消費電力の部品を提供します。 ユーザーは、ワンタイムプログラマブル(OTP)不揮発性メモリ(NVM)をプログラミングして、SLG46620-EVの相互接続ロジック、IOピン、高電圧ピン、およびマクロセルを構成することにより、回路設計を実現します。 この汎用性の高いデバイスにより、様々なミックスド・シグナル機能を非常に小さく、低消費電力の単一集積回路内で設計することができます。

パラメータ

| 属性 | 値 |

|---|---|

| Nominal VDD | 1.71 - 5.5 |

| GPIOs (#) | 18 |

| Special Features | 2x DAC, 3x PWM, ADC (8-bit SAR) |

| ACMP Channels (#) | 6 |

| DCMP | 3 |

| CNT/DLY (Max) (#) | 10 |

| Look-up Table (LUTs) | 26 |

| D Flip-flops (DFFs) (#) | 12 |

| Pipe Delay | 2 x 16-stage |

| # of Programable Delays (#) | 2 |

| Oscillator Type | RC OSC, LF OSC, Ring OSC |

| Temp. Range (°C) | -40 to +105°C |

| Interface | SPI |

| Memory Type | OTP |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFN | 2.0 x 3.0 | 20 | 0.4 |

アプリケーション

- 屋外用電子機器

- ファクトリー・オートメーション

- 電動自転車

- パワーエレクトロニクス

- EV充電ステーション

適用されたフィルター