特長

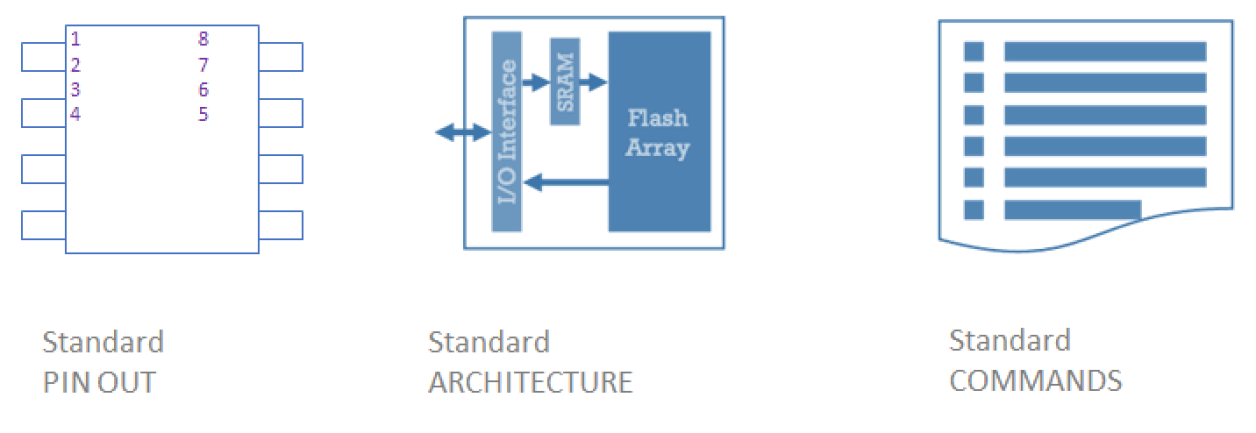

- Universally compatible pinout and command set

- Standard block architecture

- Supports Dual I/O, Quad I/O and XiP operation

- Quad enabled at the factory

- Continuous read, wrap and burst modes for XiP

説明

The AT25QF641B is a member of our standard class code and data storage solutions designed for 3V systems in which program code is shadowed from Flash memory into embedded or external RAM for execution.

The architecture includes erase block sizes that are optimized to meet the needs of today's code and data storage applications and three security register pages for unique device serialization, system-level Electronic Serial Number (ESN) storage, locked key storage, etc

パラメータ

| 属性 | 値 |

|---|---|

| Memory Class | Standard Flash |

| Memory Density | 64 |

| Operating Voltage Range (V) | 2.7 - 3.6 |

| Speed | 133 MHz |

| Interface | Quad SPI (default), Single, Dual |

| Temp. Range (°C) | -40 to +85°C |

| Deep Power Down (µA) | 1 |

| Read Current (mA) | 3.3 |

| Key Benefit | Standard features |

アプリケーション・ブロック図

| コードレスブラシレスモータドリル コードレスブラシレスモータドリルの設計が、パワー、精度、そして接続性を実現します。 |

| デジタル制御式自動エスプレッソメーカー 大型タッチスクリーンとスマートクラウド接続を備えたAI搭載エスプレッソマシン。 |

適用されたフィルター