特長

- A and C speeds

- Typical tSK(o) (output skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015

- > 200V using machine model (C = 200pF, R = 0)

- VCC = 3.3V ± 0.3V, normal range, or VCC = 2.7V to 3.6V, extended range

- CMOS power levels (0.4µW typ. static)

- Rail-to-rail output swing for increased noise margin

- Low ground bounce (0.3V typ.)

- Inputs (except I/O) can be driven by 3.3V or 5V components

- Available in 48-pin SSOP and TSSOP packages

説明

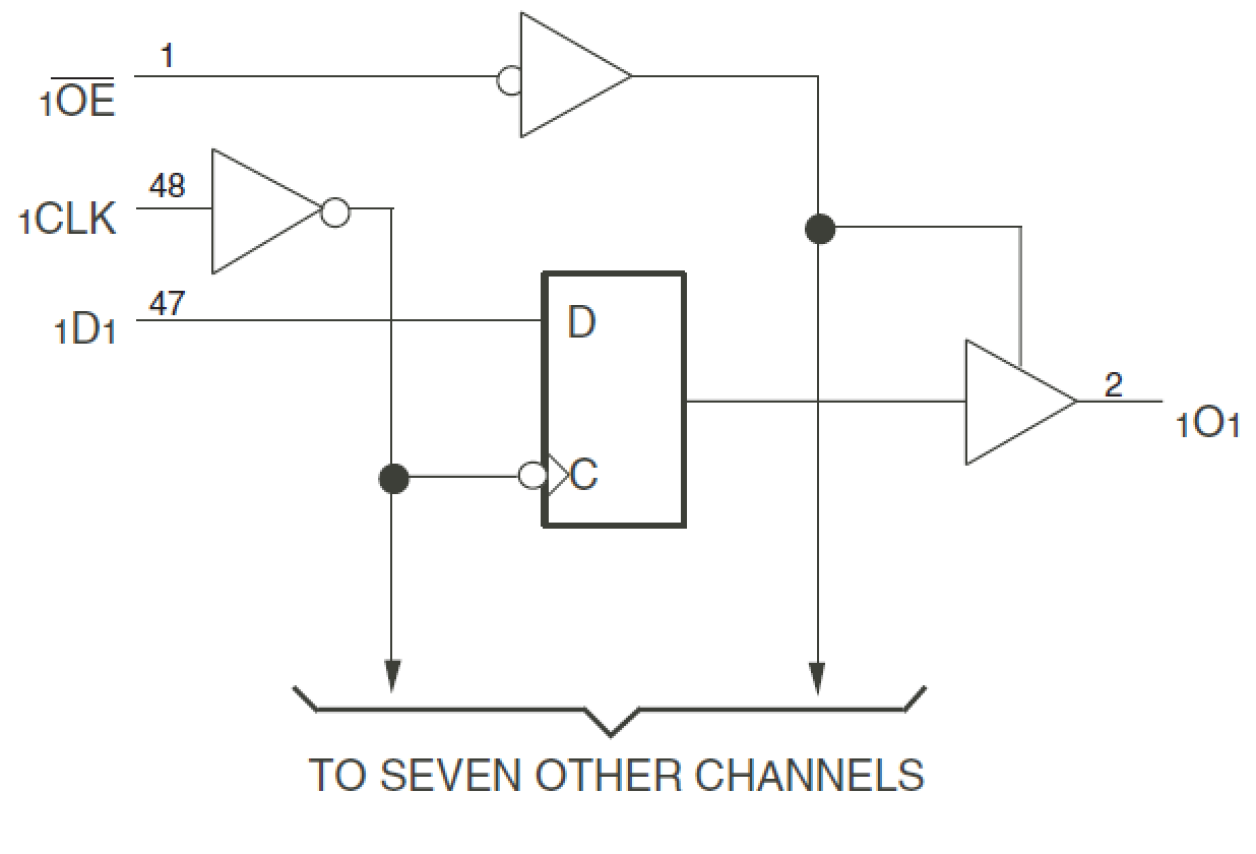

The 74FCT163374 16-bit high-speed, low-power edge-triggered D-type register is ideal for use as buffer registers for data synchronization and storage. The Output Enable (xOE) and clock (xCLK) controls are organized to operate each device as two 8-bit or one 16-bit register with a common clock. The inputs of 74FCT163374 can be driven from either 3.3V or 5V devices which allows for the use as translators in a mixed 3.3V/ 5V supply system. The 74FCT163374 operates at -40 °C to +85 °C.

パラメータ

| 属性 | 値 |

|---|---|

| Function | Register |

| Pkg. Code | PAG48 |

| Temp. Range (°C) | -40 to 85°C |

| Bus Width (bits) | 16 |

| Core Voltage (V) | 3.3 |

| Output Type | 3-state |

| Speed Grade | C |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TSSOP | 12.5 x 6.1 x 1.0 | 48 | 0.5 |

適用されたフィルター