特長

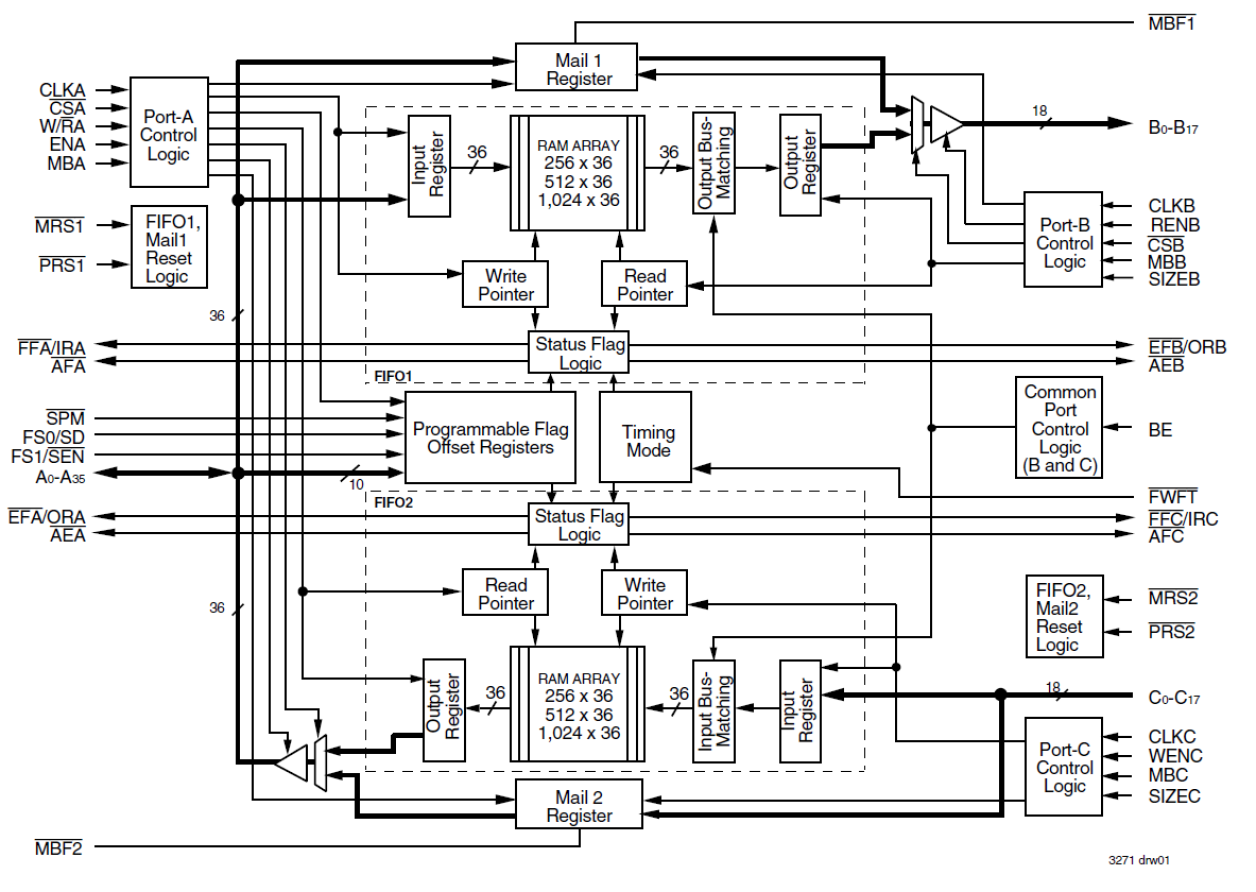

- Two independent FIFOs buffer data between one bidirectional 36-bit port and two unidirectional 18-bit ports

- 18-bit (word) and 9-bit (byte) bus sizing of 18 bits (word)

- Programmable Almost-Empty and Almost-Full flags

- Serial or parallel programming of partial flags

- Master Reset clears data and configures FIFO, Partial Reset clears data but retains configuration settings

- Mailbox bypass registers for each FIFO

- Auto power down minimizes power dissipation

- Available in 128-pin TQFP package

- Industrial temperature range (–40C to +85C) is available

説明

The 723636 is a 512 x 36 x 2 Triple Bus sync FIFO memory which supports clock frequencies up to 83 MHz and has read access times as fast as 8 ns. FIFO data can be read out and written using either 18-bit or 9-bit formats with a choice of Big- or Little-Endian configurations. The clocks for each port are independent of one another and can be asynchronous or coincident. These devices can operate in the IDT Standard mode or First Word Fall Through mode.

適用されたフィルター