Features

- SAR ADC

- Selectable Resolution: 14-, 12-, 10-, 8-bit

- Up to 2.35Msps in 8-bit mode

- Sampling up to Four Analog Channels

- Output Options: Parallel, I2C, SPI

- Programmable Gain Amplifier

- Gain Range: 1x to 64x

- Supports Differential and Single-Ended Modes

- MathCore

- Multiplier, Adder, Subtractor, Shifter

- Four Independent Data Buffers

- Buffer Length: up to Eight 16-bit Words

- Modes: Oversampling, Moving Average, Counter Capture

- Memory Table Macrocell

- 4096 Words × 12-bit

- Modes: Full Range or Two Ranges

- Supports ADC Data Linearization or Custom y = F(x)

- ADDR-to-DATA / Storage Modes

- 16-bit Multichannel Digital Comparator (MDCMP)

- Up to Four Independent Channels

- Static or Dynamic Threshold

- Hysteresis Option for Each Channel

- PWM Macrocell

- 12-bit Resolution

- Dynamic Duty Cycle Change (up to 4096 values)

- Width Converter Macrocell

- 12-bit Parallel Data Output

- Optional Output: 12×1-bit, 6×2-bit, 3×4-bit

- 12-bit DAC

- 333ksps Digital-to-Analog Converter

- Selectable Current Source

- Integrated Voltage References (VREF)

- High Speed Analog Comparator

- Configurable Hysteresis and Reference

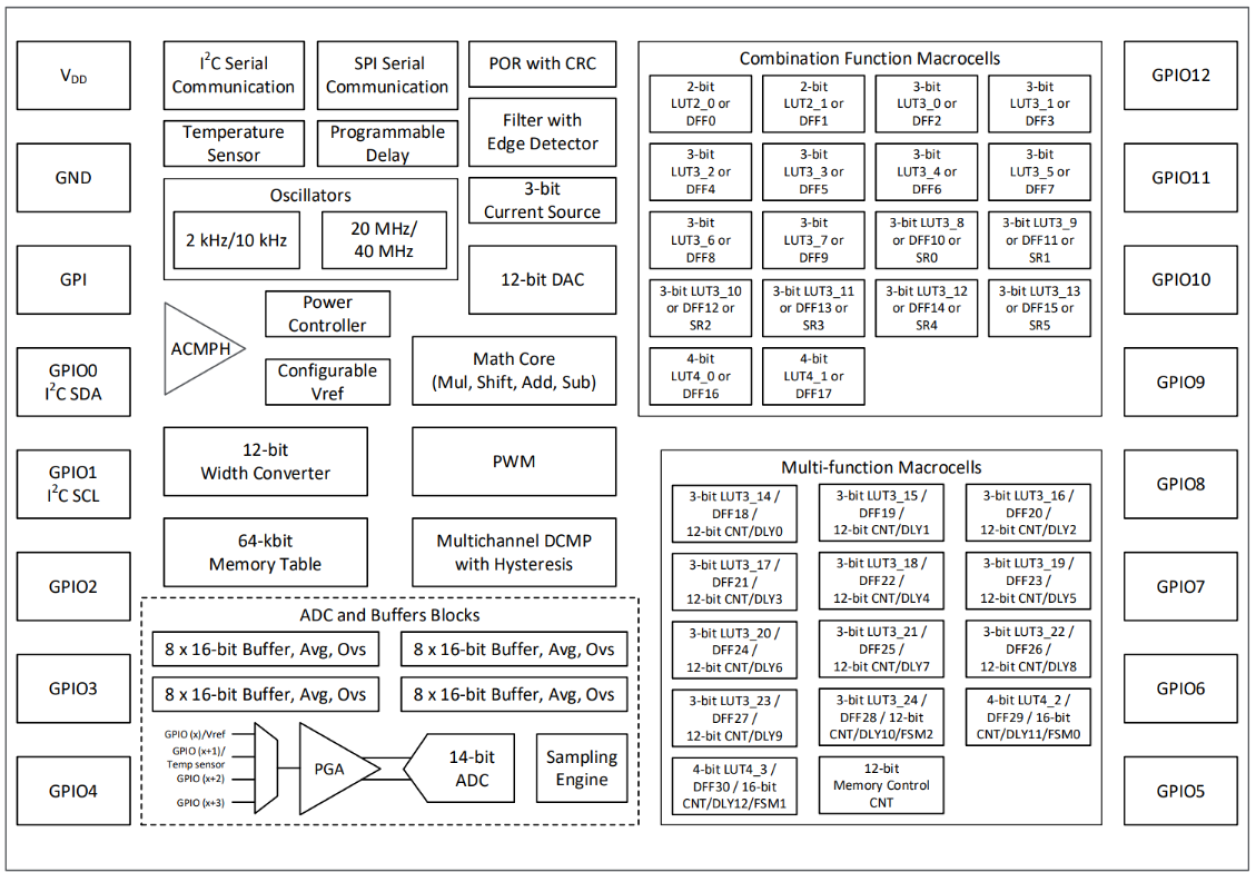

- Combination Function Macrocells (18 total)

- 2×2-bit LUT or DFF/LATCH

- 8×3-bit LUT or DFF/LATCH with Set/Reset

- 6×DFF/LATCH or 3-bit LUT or Shift Registers

- 2×4-bit LUT or DFF/LATCH with Set/Reset

- Multi-Function Macrocells (14 total)

- 10× DFF/LATCH or 3-bit LUT + 12-bit Delay/Counter

- 2× DFF/LATCH or 4-bit LUT + 16-bit Delay/Counter/FSM

- 1× DFF/LATCH or 3-bit LUT + 12-bit Delay/Counter/FSM

- 12-bit Memory Control Up/Down Counter

- Communication Interfaces

- I2C Interface

- SPI Interface

- Logic and Timing

- Programmable Delay with Edge Detector Output

- Deglitch Filter or Edge Detector

- Oscillators (OSC)

- 2kHz/10kHz

- 20MHz/40MHz

- Analog Temperature Sensor

- Power-On Reset (POR) with CRC

- Read Back Protection (Read Lock)

- Power Supply

- 1.71V to 3.6V

- Operating Temperature

- -40°C to +105°C

- Compliance

- RoHS Compliant/Halogen-Free

- Available Package

- 16-pin STQFN: 2.0mm × 2.0mm × 0.55mm, 0.4mm pitch

Description

The SLG47011-E provides a small, low-power solution for commonly used analog-to-digital conversion and mixed-signal functions. A flexible data acquisition system used in conjunction with configurable logic provides a way to implement a wide variety of functions with minimal cost. The user can create a circuit design by programming the one-time programmable (OTP) non-volatile memory (NVM), to configure the interconnect logic, the macrocells, and the IO pins.

Parameters

| Attributes | Value |

|---|---|

| GPIOs (#) | 14 |

| Special Features | ADC (14-bit, SAR), DAC (12-bit), PGA 1x-64x, Math Core, 4k x 12-bit RAM, 1x PWM |

| ACMP Channels (#) | 1 |

| DCMP | 1 |

| CNT/DLY (Max) (#) | 15 |

| Look-up Table (LUTs) | 31 |

| D Flip-flops (DFFs) (#) | 31 |

| Pipe Delay | 6x 8-bit Shift Regs |

| # of Programable Delays (#) | 1 |

| Oscillator Type | LF OSC, Ring OSC |

| Temperature Sensor (ch) (#) | 1 |

| Temp. Range (°C) | -40 to +105°C |

| Interface | I2C, SPI |

| Memory Type | OTP |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFN | 2.0 x 2.0 | 16 | 0.4 |

Product Comparison

| SLG47011-E | SLG47004 | SLG47003 | SLG47011 | |

| Special Features | 1x PWM, 4k x 12-bit RAM, ADC (14-bit, SAR), DAC (12-bit), Math Core, PGA 1x-64x | 2-Ch Auto-Trim, 2x An Switch, 2x Op Amp or 1x In-Amp, 2x Rheostat, EEPROM | 2x Op Amps, 2x Rheostats, Analog Switch | 1x-64x, 4k x 12-bit RAM, ADC (14-bit, SAR), DAC (12-bit), MathCore, PGA, PWM |

| GPIOs (#) | 14 | 8 | 15 | 14 |

| Memory Type | OTP | MTP | OTP | OTP |

| Lead Count (#) | 16 | 24 | 24 | 16 |

| Pkg. Dimensions (mm) | 2.0 x 2.0 | 3.0 x 3.0 | 3.0 x 3.0 | 2.0 x 2.0 |

| Temp. Range (°C) | -40 to +105°C | -40 to +85°C | -40 to +85°C | -40 to +85°C |

Applications

- Consumer Electronics

- Handheld and Portable Electronics

- Industrial Automation and Process Control

- Personal Computers and Servers

- PC Peripherals

- Battery Voltage and Current Monitoring

- Power Monitors

Applied Filters: