Applied Filters:

Evaluation Boards & Kits

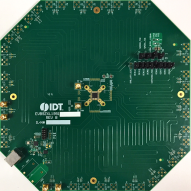

EVK9ZXL1951D Active

Evaluation Kit for 19-Output DB1900Z for PCIe Gen1-4 and QPI/UPI

The evaluation board is designed to help the customer evaluate the 9ZXL1951D. The device is programmable through an SMBus interface. The user guide details the board set and connection, as well as the companion Graphical User Interface (GUI) installation for communicating with the device. The... Read More

Recommended Documents: