特長

- WD1 (960H) and D1 compatible video decoding operation and each channel is programmable

- NTSC (M, 4.43) and PAL (B, D, G, H, I, M, N, N combination), PAL (60) support with automatic format detection

- Software selectable analog inputs allows any of 2 CVBS per one video ADC

- Built-in analog anti-alias filter

- Four 10-bit ADCs and analog clamping circuit for CVBS input

- Fully programmable static gain or automatic gain control for the Y channel

- Programmable white peak control for CVBS channel

- 4-H adaptive comb filter Y/C separation

- PAL delay line for color phase error correction

- Image enhancement with peaking and CTI

- Digital sub-carrier PLL for accurate color decoding

- Digital Horizontal PLL for synchronization processing and pixel sampling

- Advanced synchronization processing and sync detection for handling non-standard and weak signal

- Programmable hue, brightness, saturation, contrast, sharpness

- Automatic color control and color killer

- ITU-R 656 like YCbCr(4:2:2) output or time multiplexed output with 36/72/144MHz for WD1 or 27/54/108MHz for D1 format

- Integrated five audio ADCs processing and one audio DAC

- Provides multi-channel audio mixed analog output

- Support I2S/DSP Master/Slave interface for record output and playback input

- PCM 8/16-bit and u-Law/A-Law 8-bit for audio word length

- Programmable audio sample rate that covers popular frequencies of 8/16/32/44.1/48kHz

- Two-wire MPU serial bus interface

- Integrated clock PLL for 144/108MHz clock output

- Embedded video encoder

- Power save and Power down mode

- Low power consumption

- Single 27MHz crystal for all standards and both WD1 and D1 format

- 3.3V tolerant I/O

- 1.0V/3.3V power supply

- 128-pin LQFP package

説明

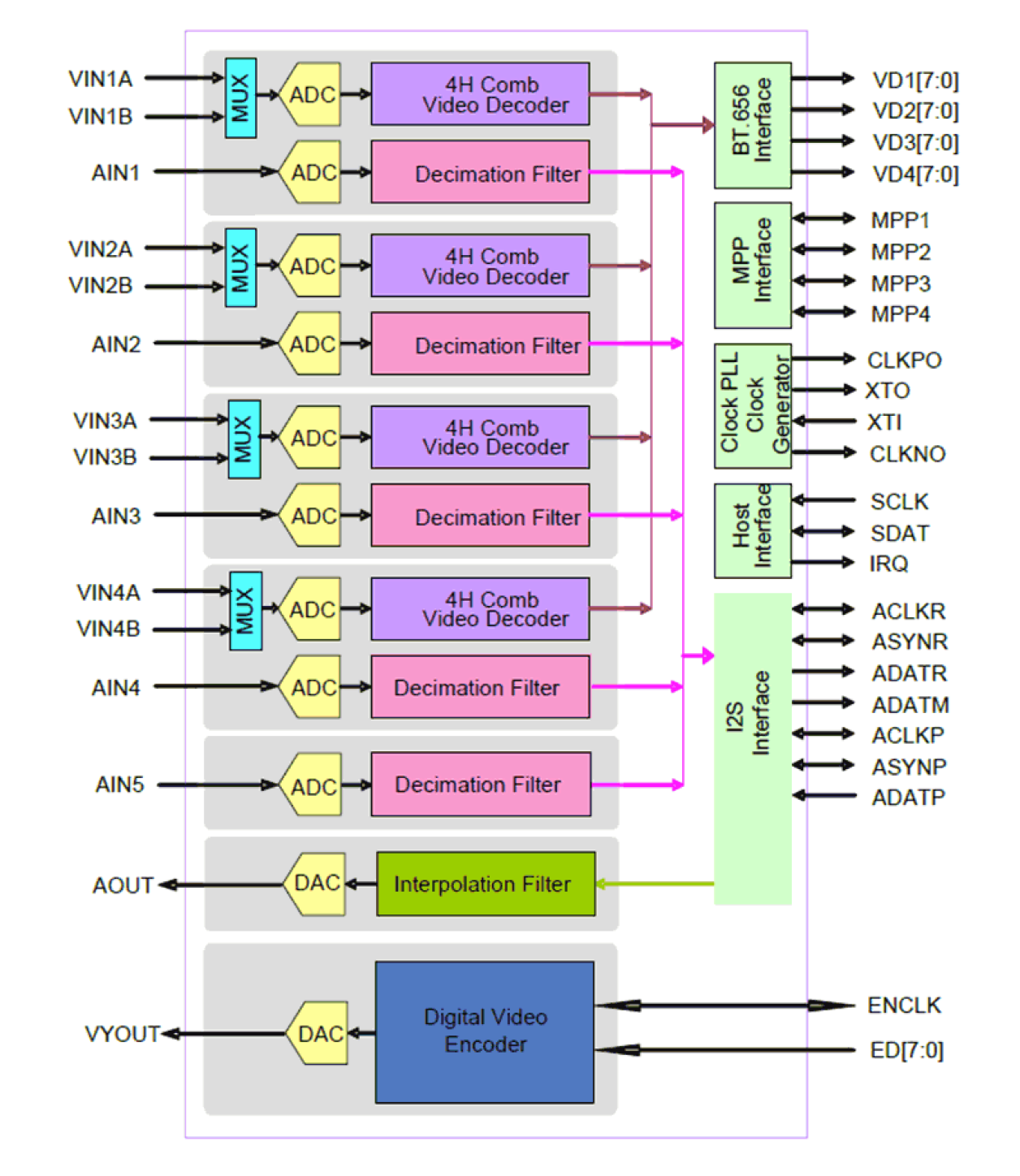

The TW2965 is a low power NTSC/PAL video decoder chip that is designed for video surveillance applications. It consumes very low power in a typical composite input application. The available power down mode further reduces the power consumption. It uses the 1. 0V for digital supply voltage and 3. 3V for I/O and analog power. A single 27MHz crystal is all that needed to decode all analog video standards. The video decoder decodes the base-band analog CVBS into digital 8-bit 4:2:2 YCbCr for output. It consists of analog front-end with input source selection, variable gain amplifier and analog-to-digital converters, Y/C separation circuit, multi-standard color decoder (PAL BGHI, PAL M, PAL N, combination PAL N, NTSC M, NTSC 4. 43) and synchronization circuitry. The Y/C separation is done with high quality adaptive 4H (5-line) comb filter for reduced cross color and cross luminance. The advanced synchronization processing circuitry can produce stable pictures for non-standard signal as well as weak signal.

適用されたフィルター