特長

- PCIe Gen1-4準拠

- 終端抵抗の内蔵により100Ωの差動Zoを実現:部品点数と基板面積を削減

- 1.8V動作:消費電力の低減

- オプションで1.05V~1.8Vの任意の電圧から出力可能:最大限の省電力を実現

- OE#端子:DIFパワーマネージメント対応

- LP-HCSL差動クロック出力:消費電力と基板面積の削減

- 各出力のスルーレートをプログラマブルに設定可能:様々な線路長に対応したチューニングが可能

- プログラマブル出力振幅:様々なアプリケーション環境に対応したチューニングが可能

- PLLがロックされるまでDIF出力をブロック:クリーンなシステムスタートアップ

- DIF出力のスプレッドは0%、-0.25%、-0.5%から選択可能:EMIの低減

- 外付け25MHz水晶振動子、0ppmの合成誤差でタイトなppmをサポート

- ストラップピンによる構成が可能:デバイス制御のためのSMBusインタフェースは不要

- 3.3VトレラントSMBusインタフェースは、レガシーコントローラに対応

- 6×6 mmの48ピンVFQFPNで、基板面積を最小限に抑えた省スペース設計

- 選択可能なSMBusアドレス:複数のデバイスでSMBusセグメントを簡単に共有

- AEC-Q100準拠、グレード2(-40℃~+105℃)バージョンで提供(ウェッタブルフランクパッケージ)

説明

9FGV0841は、PCIe Gen1–4アプリケーション用の8出力の超低消費電力クロックジェネレータで、Zo=100Ωの出力終端を内蔵しています。 クロック管理用に8つの出力イネーブルを備え、スペクトラム拡散オフに加えて2種類のスペクトラム拡散レベルをサポートします。

評価ボードや材料に関する情報は、お近くの販売代理店にお問い合わせください。

パラメータ

| 属性 | 値 |

|---|---|

| Diff. Outputs | 8 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 25 - 25, 100 - 100 |

| Power Consumption Typ (mW) | 62 |

| Supply Voltage (V) | 1.8 - 1.8 |

| Output Type | LP-HCSL, LVCMOS |

| Xtal Freq (MHz) | 25 - 25 |

| Diff. Termination Resistors | 0 |

| Package Area (mm²) | 36 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 25 - 25 |

| Function | Generator |

| Input Type | Crystal, LVCMOS |

| Core Voltage (V) | 1.8 |

| Output Voltage (V) | 0.8V, 1.8V |

| Product Category | Automotive Timing, PCI Express Clocks |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 6.0 x 6.0 x 0.9 | 48 | 0.4 |

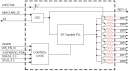

アプリケーション・ブロック図

| コネクテッドAndroidベースの車両インストルメントクラスタ ワイヤレス接続とリアルタイムディスプレイを備えたAndroidベースの自動車コックピット。 |

| 通信ゲートウェイおよび統合DVR/DMSシステム CoGWとDVR/DMSビデオ処理を統合した統合車載ゲートウェイ。 |

| ハプティクスを備えた自動車コックピットシステム 次世代の触覚、BroadLEDドライバ、PMICを備えた高度なコックピットシステム。 |

| タイヤ空気圧監視システム PMICを内蔵した低電力Bluetooth LE TPMS設計により、コスト、サイズ、開発時間を短縮します。 |

| フルグラフィックス クラスタ&コックピットシステム 自動車のコックピットでフルグラフィックス クラスタをサポートする高効率ディスプレイシステム。 |

| ハイエンドコックピット&インフォテインメントソリューション |

| 4Kビデオをサポートするフル機能HMI 高性能HMI設計により、シームレスな4Kビデオ、高度なグラフィックス、および信頼性の高いコネクティビティを実現します。 |

| FHDビデオをサポートするフル機能HMI フル機能のHMIプラットフォームは、高性能MPUを備え、USB 3.0、PCI Express、およびギガビットイーサネットインタフェースを内蔵しています。 |

適用されたフィルター