特長

- Four low skew, low additive jitter LVDS output pairs

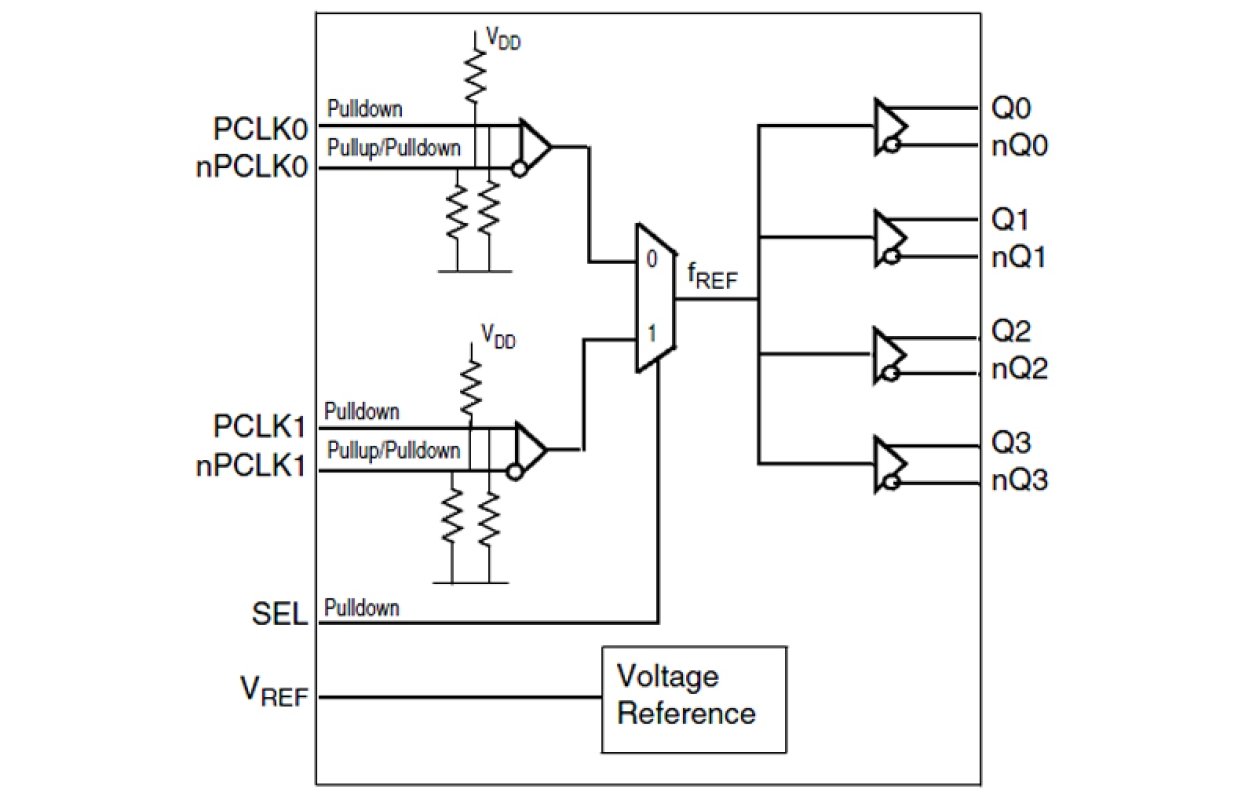

- Two selectable, differential clock input pair

- Differential CLK, nCLK pairs can accept the following differential input levels: LVDS, CML

- Maximum input clock frequency: 1.5GHz

- Output skew: 10ps (typical)

- Propagation delay: 400ps (maximum)

- Low additive phase jitter, RMS; fREF = 156.25MHz, 10kHz to 20MHz: 34fs (typical)

- Device current consumption (IDD):

- 65mA typical: 1.8V

- 75mA typical: 2.5V

- Full 1.8V or 2.5V supply voltage

- Lead-free (RoHS 6), 16-lead VFQFN package

- -40 °C to 85 °C ambient operating temperature

- Supports case temperature up to +105 °C

- Supports PCI Express Gen 1-5

説明

The 8P34S1204 is a high-performance differential LVDS fanout buffer. The device is designed for the fanout of 1PPS signals or high-frequency, very low additive phase-noise clock and data signals. The 8P34S1204 supports fail-safe operation and is characterized to operate from a 1.8V or 2.5V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 8P34S1204 ideal for those clock distribution applications demanding well-defined performance and repeatability. Two selectable differential inputs and four low skew outputs are available. The integrated bias voltage reference enables easy interfacing of single-ended signals to the differential device input. The device is optimized for low power consumption and low additive phase noise.

パラメータ

| 属性 | 値 |

|---|---|

| Temp. Range (°C) | -40 to 85°C |

| Product Category | Clock Buffers & Drivers, Clock Multiplexers, RF Buffers |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 3.0 x 3.0 x 1.0 | 16 | 0.5 |

適用されたフィルター