パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PNG64 |

| Lead Count (#): | 64 |

| Pkg. Dimensions (mm): | 14.0 x 14.0 x 1.4 |

| Pitch (mm): | 0.8 |

環境及び輸出分類情報

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.32.0071 |

製品スペック

| Lead Count (#) | 64 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Country of Assembly | TAIWAN |

| Country of Wafer Fabrication | TAIWAN, USA |

| Architecture | Uni-directional |

| Bus Width (bits) | 9 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 4096 |

| Family Name | SuperSync |

| I/O Frequency (MHz) | 100 - 100 |

| I/O Type | 3.3 V LVTTL |

| Interface | Synchronous |

| Length (mm) | 14 |

| MOQ | 45 |

| Organization | 512K x 9 |

| Package Area (mm²) | 196 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 14.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Price (USD) | $228.17133 |

| Qty. per Carrier (#) | 90 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

72V2111 に関するリソース

説明

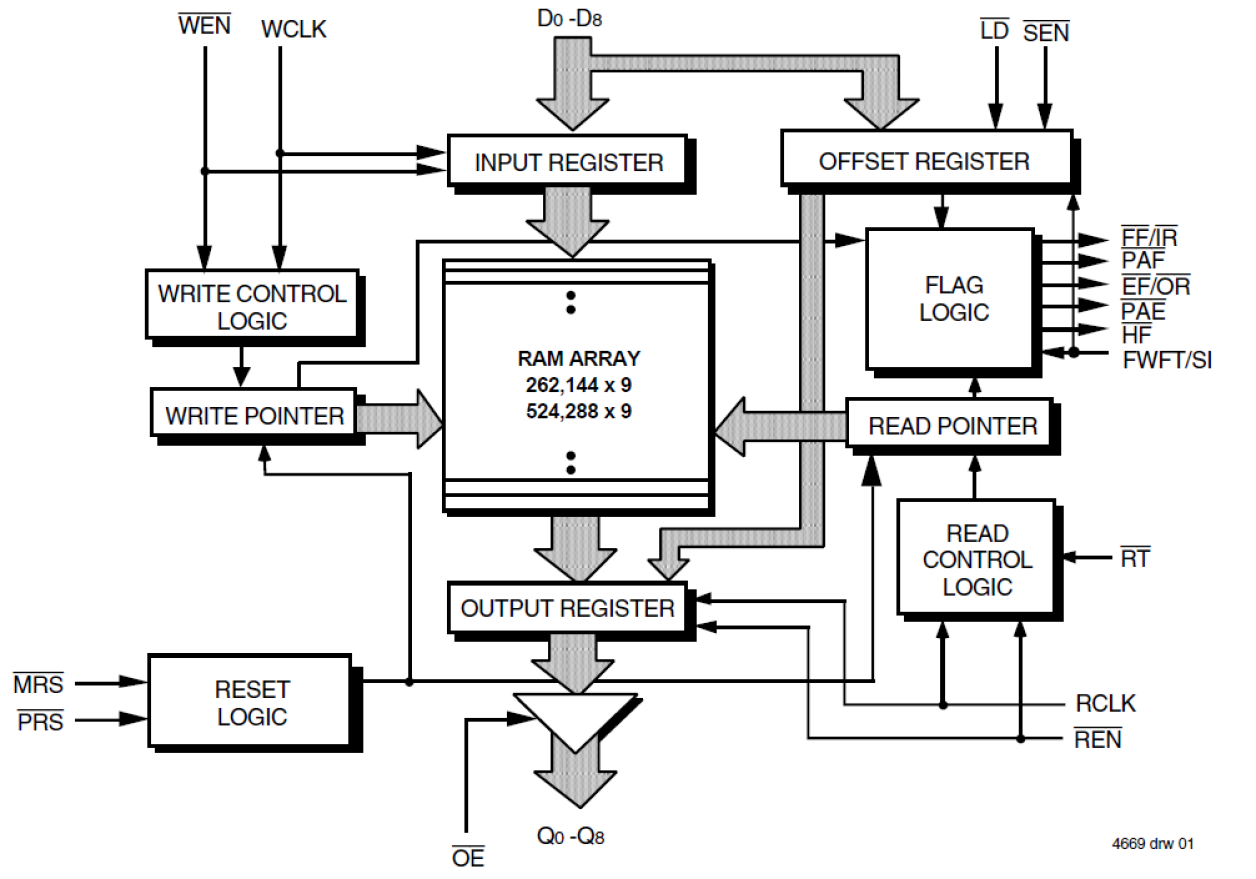

The 72V2111 is a 16K x 9 SuperSync FIFO memory with clocked read and write controls. The Frequency Select pin (FS) has been removed, thus it is no longer necessary to select which of the two clock inputs, Read Clock (RCLK) or Write Clock (WCLK), is running at the higher frequency. The period required by the retransmit operation and the first word data latency period is now fixed and short; the variable clock cycle counting delay associated with the latency period found on previous SuperSync devices has been eliminated on this SuperSync family.