Features

- PCIe Gen 1–7 compliance

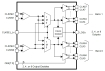

- 2:8 multiplexer or two 4-output buffer options

- Drive both source-terminated and double-terminated loads

- Selectable 34Ω, 85Ω, and 100Ω output impedance

- Power down tolerance (PDT)

- Flexible startup sequencing (FSS)

- Automatic clock parking (ACP)

- Dedicated OE# pins to control group output

- 6mm × 6mm 48-VFQFPN package

Description

The RC19308 is a 2:8 PCIe Gen7 multiplexer that is backward compatible with earlier PCIe generations. The RC19308 provides ultra-low additive jitter and reduced in-to-out delay performance for better design margin and incorporates several features for easier and more robust design.

Parameters

| Attributes | Value |

|---|---|

| Diff. Outputs | 8 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 1 - 400 |

| Diff. Inputs | 1 |

| Power Consumption Typ (mW) | 391 |

| Supply Voltage (V) | 1.8 - 1.8 |

| Output Type | LP-HCSL |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 1 - 400 |

| Adjustable Phase | No |

| Noise Floor (dBc/Hz) | -154 |

| Channels (#) | 2 |

| Additive Phase Jitter Typ RMS (fs) | 42.8 |

| 105°C Max. Case Temp. | 1 |

| Function | Multiplexer |

| Input Type | LVDS, HCSL |

| Output Banks (#) | 2 |

| Core Voltage (V) | 1.8 |

| Output Voltage (V) | 0.8 |

| Product Category | PCI Express Clocks |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 6.0 x 6.0 x 0.9 | 48 | 0.4 |

Applications

- Cloud/High-performance computing

- nVME storage

- Networking

- Accelerators

Applied Filters: