Introduction

As all designers know, when selecting timing devices for board design, it is important to know the phase noise performance. The problem is that Phase Noise Analyzers (PNA) are not readily available to everyone. For programmable timing devices, especially, users would want to see the performance for a particular configuration. Renesas Programmable Clocks Live Bench Measurement tool makes it simple and convenient for anyone to evaluate the performance of its flagship clocks and timing families, such as VersaClock®, FemtoClock™, and ProXO.

Quick, Accurate Results

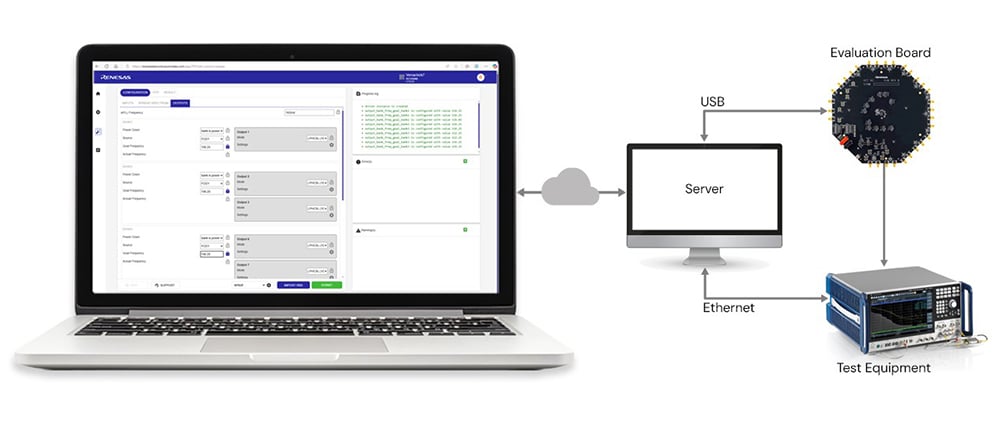

The Live Bench Measurement tool allows users to configure devices and deliver live phase noise measurements with no boards or lab equipment needed. These measurements mimic what one would get in a live lab setting, but with 24/7 access, no reservations required, and no hassle of submitting technical support tickets for each use.

Software Input

Users can import existing .rbs (configuration) files from the RICBox GUI or create a configuration from scratch within the tool. Then, users can request an automated phase noise measurement. Most Renesas clocks can support multiple configurations. For example, VersaClock 7 allows up to 27 configurations reusable across multiple designs and may be stored in on-chip One-Time Programmable (OTP) memory or external I2C EEPROM. The tool also supports multiple configurations measurements. Once qualified, the same part number can be used across different platforms.

Software Output

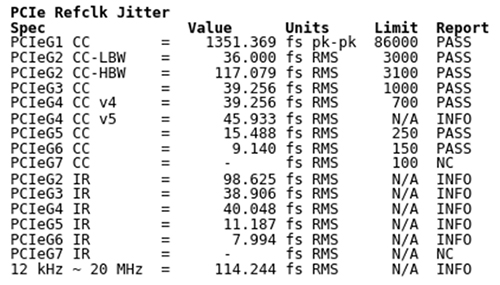

Summary results will be provided in .txt, .csv, and .rbs formats. Phase noise screen captures, both normalized and omit spurs phase noise, and the data offset vs. phase noise format for each output. For inputs of 100MHz HCSL, the PCIe jitter data will be calculated, which includes PCIe plots comparing different specs for each PCIe generation. Orderable part numbers can then be generated, and sample requests can be placed.

Designed to Help Board Designers

With Renesas' Programmable Clocks Live Bench Measurement tool, evaluating phase noise is no longer limited by lab access or equipment. Users can configure devices and view live, lab-quality measurements from anywhere—no hardware, no wait, no hassle. It's an effortless way to assess performance across VersaClock, FemtoClock, and ProXO families—anytime, 24/7.

Resources

Visit the Programmable Clocks Live Bench Measurement tool to begin configuring today! To learn more about Renesas clocks and timing families, visit: