特長

- Nine differential 2.5V, 3.3V LVPECL/ECL outputs

- Selectable differential CLK, nCLK or LVPECL clock inputs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- PCLK, nPCLK supports the following input types: LVPECL, LVDS, CML, SSTL

- Output frequency: 1.6GHz (maximum)

- Translates any single-ended input signal (LVCMOS, LVTTL, GTL) to 3.3V LVPECL levels with resistor bias on nCLK or nPCLK inputs

- Output skew: 20ps (typical)

- Part-to-part skew: 90ps (typical)

- Propagation delay: 885ps (typical), PCLK

- LVPECL mode operating voltage supply range: VCC = 2.375V to 3.465V, VEE = 0V

- ECL mode operating voltage supply range: VCC = 0V, VEE = -3.465V to -2.375V

- -40°C to 85°C ambient operating temperature

- Available lead-free (RoHS 6) package

説明

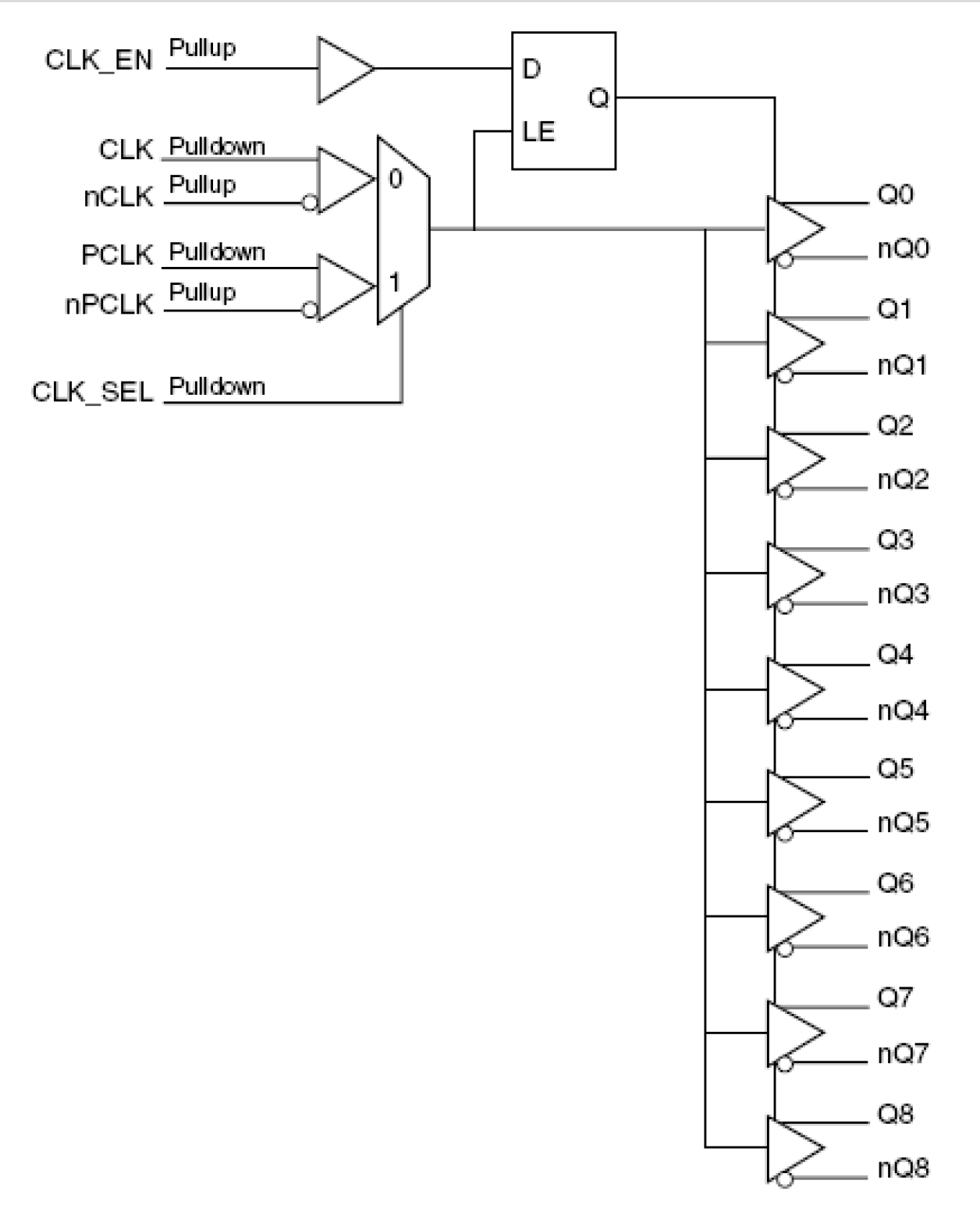

The 853S031I is a low skew, high performance 1-to-9 Differential-to-2.5V/3.3V LVPECL/ECL Fanout Buffer. The 853S031I has two selectable clock inputs. The CLK, nCLK pair can accept most standard differential input levels. The PCLK, nPCLK pair can accept LVPECL, LVDS, CML or SSTL input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. Guaranteed output and part-to-part skew characteristics make the 853S031I ideal for high performance workstation and server applications.

パラメータ

| 属性 | 値 |

|---|---|

| Temp. Range (°C) | -40 to 85°C |

| Product Category | Clock Buffers & Drivers, Clock Multiplexers |

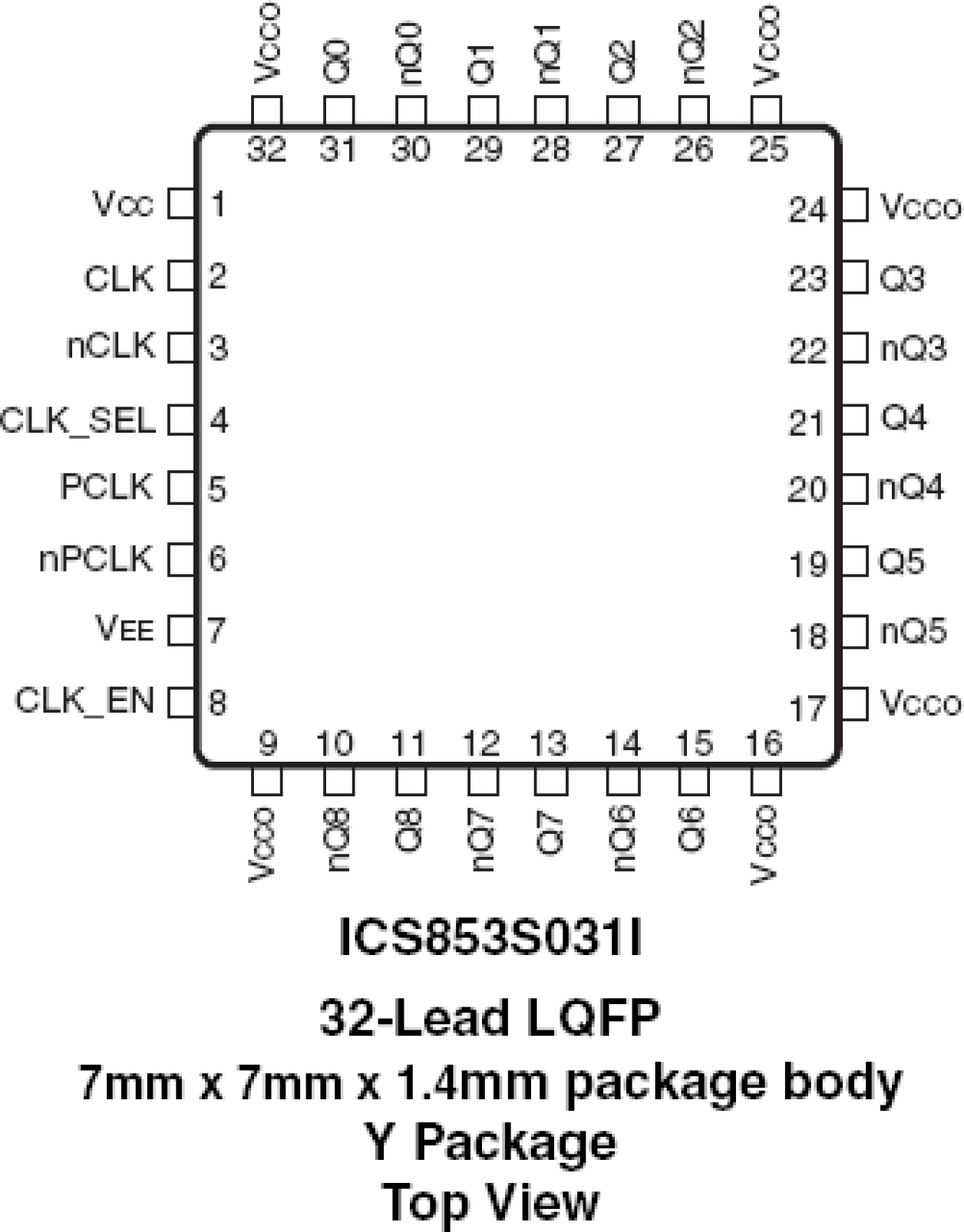

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFP | 7.0 x 7.0 x 1.4 | 32 | 0.8 |

適用されたフィルター