Features

- High system speed 150MHz (3.8ns clock access time)

- LBO input selects interleaved or linear burst mode

- Self-timed write cycle with global write control (GW), byte write enable (BWE), and byte writes (BWx)

- 3.3V core power supply

- Power down controlled by ZZ input

- 3.3V I/O

- Available in 100 -pin TQFP package

Description

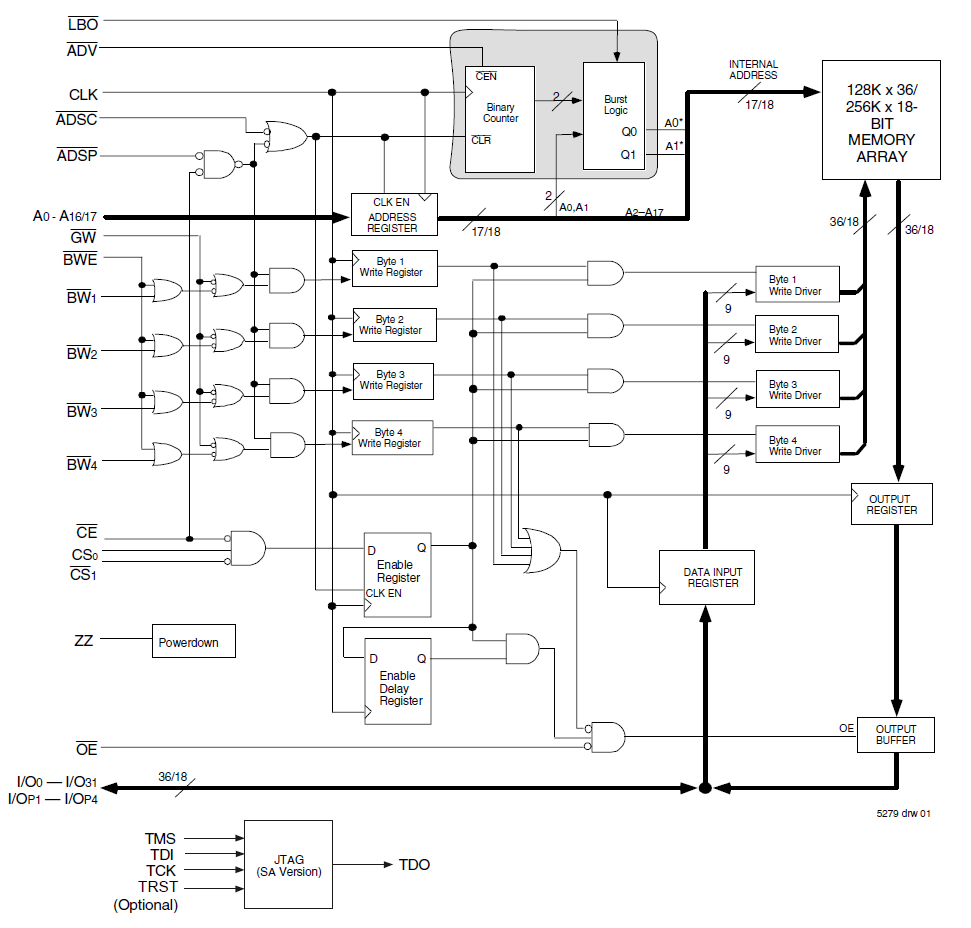

The 71V3578 3.3V CMOS SRAM is organized as 256K x 18. The 71V3578 SRAM contains write, data, address and control registers. The burst mode feature offers the highest level of performance to the system designer, as it can provide four cycles of data for a single address presented to the SRAM.

Parameters

| Attributes | Value |

|---|---|

| Density (Kb) | 4608 |

| Bus Width (bits) | 18 |

| Core Voltage (V) | 3.3 |

| Pkg. Code | PKG100 |

| Organization | 256K x 18 |

| I/O Voltage (V) | 3.3 - 3.3 |

| I/O Frequency (MHz) | 150 - 150 |

| Temp. Range (°C) | -40 to 85°C |

| Architecture | Synch Burst |

| Output Type | Pipelined |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TQFP | 20.0 x 14.0 x 1.4 | 100 | 0.65 |

Applied Filters:

Loading