特長

- PCIe Gen1-4準拠

- 終端内蔵LP-HCSL出力;標準的なPCIeデバイスと比較して24個の抵抗を節約可能

- 標準消費電力54mW;熱に関する懸念を低減

- 出力はオプションで1.05〜1.8Vの任意の電圧から出力可能;最大限の省電力を実現

- OE#ピン;DIFパワーマネージメント対応

- 各出力のプログラマブルスルー・レート;様々な線長に合わせたチューニングが可能

- プログラマブル出力振幅;様々な使用環境に合わせたチューニングが可能

- PLLがロックされるまでのDIF出力;クリーンなシステムスタートアップ

- 0%、-0.25%、-0.5%から選択可能なDIF出力スプレッド;EMIの低減

- 外付け25MHz水晶振動子、0ppmの合成エラーでタイトなppmをサポート

- ストラップピンによるコンフィギュレーションが可能;デバイス制御にSMBusインタフェースは不要

- 3.3 VトレラントSMBusインタフェースは、レガシーコントローラに対応

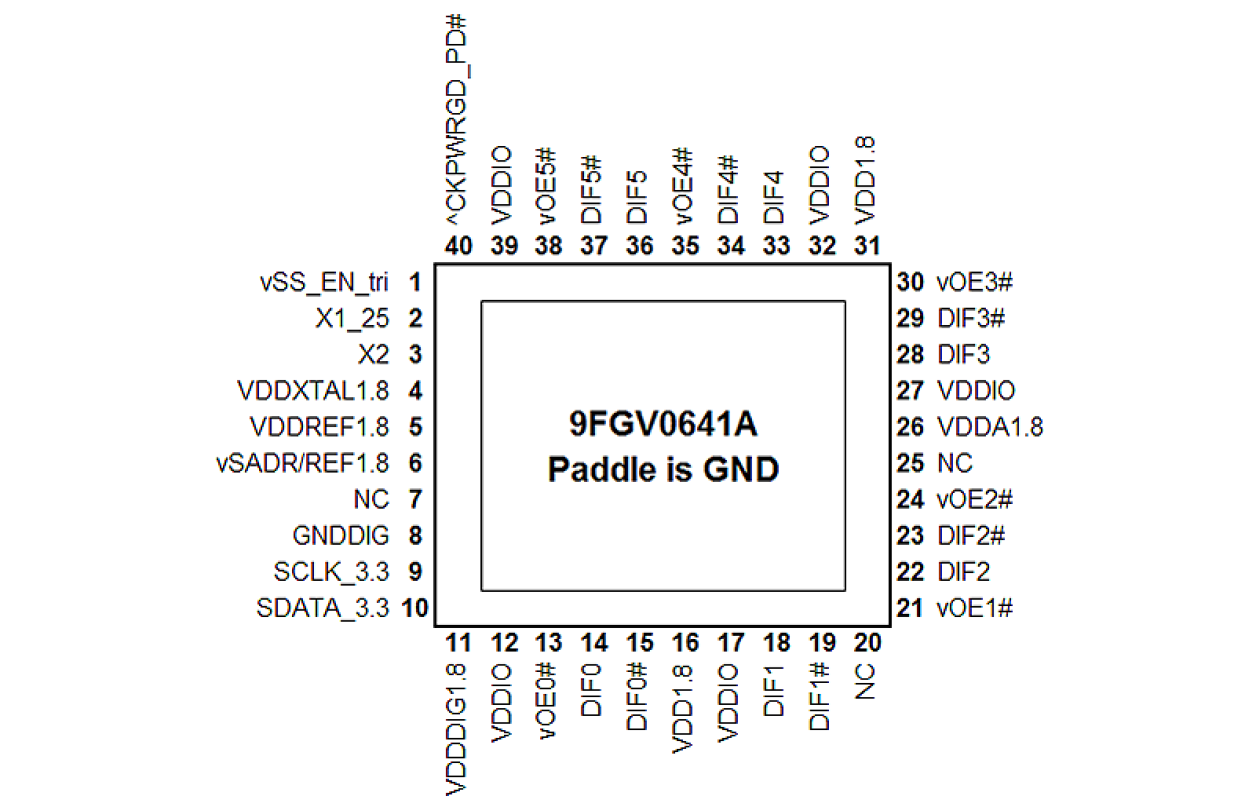

- 省スペースな5×5mm 40ピンVFQFPN;最小限の基板スペースを実現

- 選択可能なSMBusアドレス;複数のデバイスでSMBusセグメントを簡単に共有可能

説明

9FGV0641は、ルネサスのSOC対応 1.8V超低消費電PCIeクロックファミリーのひとつです。 このデバイスは100Ωの出力終端を内蔵しており、100Ωの伝送ラインに方向性を持たせて接続することができます。 また、クロック管理用に6つの出力イネーブルを備え、スペクトラム拡散オフに加えて2種類のスペクトラム拡散レベルにも対応しています。

評価ボードや材料に関する情報は、お近くの販売代理店にお問い合わせください。

パラメータ

| 属性 | 値 |

|---|---|

| Diff. Outputs | 6 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 25 - 25, 100 - 100 |

| Power Consumption Typ (mW) | 54 |

| Supply Voltage (V) | 1.8 - 1.8 |

| Output Type | LP-HCSL, LVCMOS |

| Xtal Freq (MHz) | 25 - 25 |

| Diff. Termination Resistors | 0 |

| Package Area (mm²) | 25 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 25 - 25 |

| Function | Generator |

| Input Type | Crystal, LVCMOS |

| Core Voltage (V) | 1.8 |

| Output Voltage (V) | 0.8V, 1.8V |

| Product Category | PCI Express Clocks |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 5.0 x 5.0 x 0.9 | 40 | 0.4 |

アプリケーション・ブロック図

| AI 搭載のスケーラブルな HMI SMARC SoM マルチコア処理、高度なグラフィックス、スマートHMIのための安定な接続性を備えたスケーラブルなSoM。 |

| 高性能ヒューマンマシンインタフェース(HMI)システム 幅広いヒューマンマシンインタフェース機能を駆動するための汎用性の高いシステムオンモジュール(SoM)。 |

| マルチディスプレイHMI SoM 消費電力とタイミングを最適化したSOMは、マルチディスプレイの組み込みアプリケーションをサポートします。 |

適用されたフィルター