パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NDG40 |

| Lead Count (#): | 40 |

| Pkg. Dimensions (mm): | 5.0 x 5.0 x 0.9 |

| Pitch (mm): | 0.4 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Pkg. Type | VFQFPN |

| Lead Count (#) | 40 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Pkg. Dimensions (mm) | 5.0 x 5.0 x 0.9 |

| Qty. per Reel (#) | 0 |

| Diff. Outputs | 8 |

| Input Type | LVDS, LP-HCSL, LVCMOS |

| Outputs (#) | 16 |

| Package Area (mm²) | 25 |

| Qty. per Carrier (#) | 490 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Programmable Clock |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, PCIe Gen6, PCIe Gen7 |

| Application | Data Center Accelerators, Switches, Routers, Synchronous Ethernet |

| Architecture | Common, SRIS, SRNS |

| C-C Jitter Max P-P (ps) | 50 |

| Channels (#) | 1 |

| Core Voltage (V) | 1.8V, 2.5V, 3.3V |

| Diff. Inputs | 2 |

| Diff. Output Signaling | LP-HCSL, LVDS, LVPECL, LVCMOS |

| Family Name | VersaClock® 7 |

| Fractional Output Dividers (#) | 3 |

| Function | Generator |

| Input Freq (MHz) | 1 - 650 |

| Inputs (#) | 2 |

| Length (mm) | 5 |

| Longevity | 2040 4月 |

| MOQ | 490 |

| Output Banks (#) | 6 |

| Output Freq Range (MHz) | 0.001 - 650 |

| Output Impedance | 85, 100 |

| Output Skew (ps) | 30 |

| Output Type | LVDS, LP-HCSL, LVCMOS |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Phase Jitter Typ RMS (fs) | 150 |

| Phase Jitter Typ RMS (ps) | 0.15 |

| Pitch (mm) | 0.4 |

| Power Consumption Typ (mW) | 1000 |

| Price (USD) | $5.47063 |

| Product Category | VersaClock, Ultra-Low Jitter Clocks (<300 fs RMS), PCI Express Clocks, Programmable Clocks |

| Prog. Clock | Yes |

| Prog. Interface | OTP, I2C, SPI, SMBUS, EEPROM |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Supply Voltage (V) | 1.8 - 1.8, 2.5 - 2.5, 3.3 - 3.3 |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 5 |

RC210 に関するリソース

説明

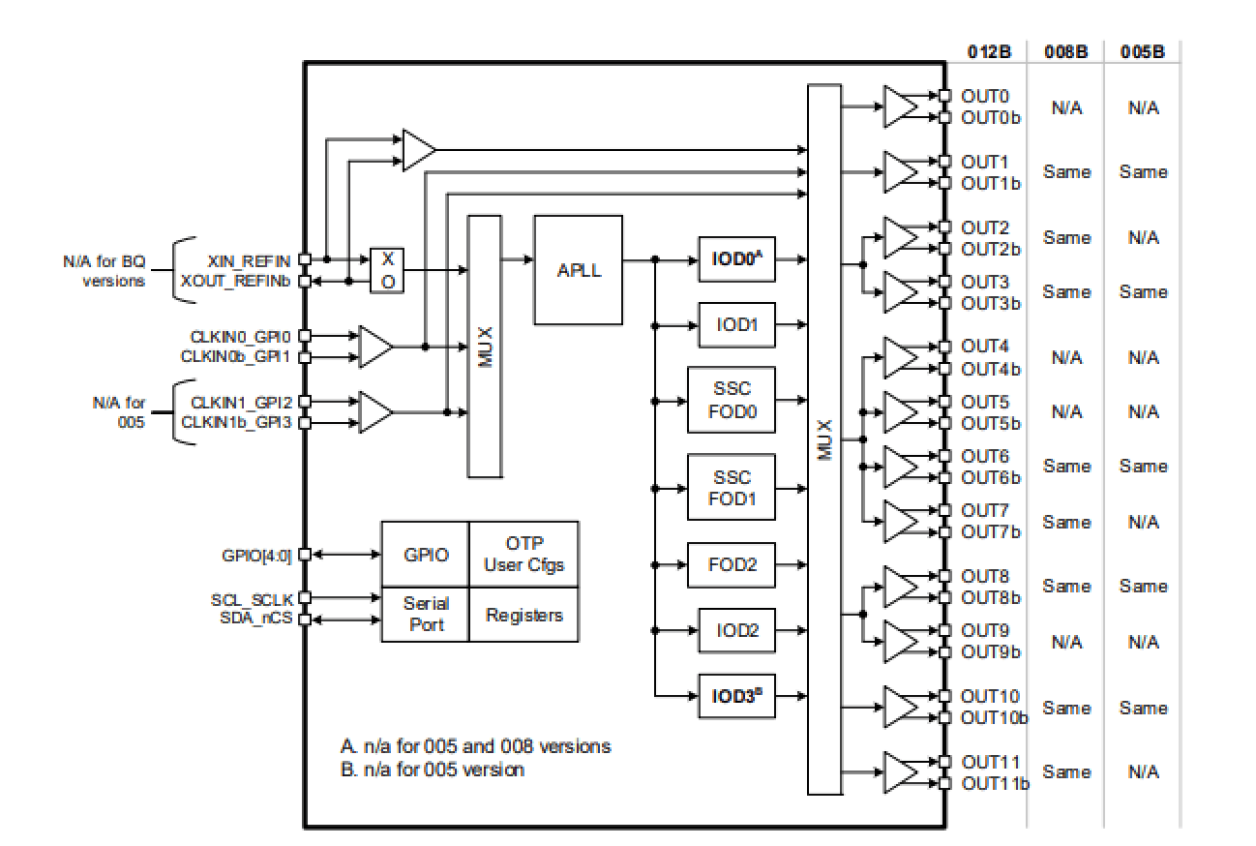

RC21xxxA(RC21012A、RC21008A)は、ルネサスのVersaClock® 7プログラマブルクロックジェネレータファミリの製品です。 ハイパフォーマンス・コンピューティング、データ通信、産業機器向けアプリケーションを対象としており、ジッタ性能150fs RMS(標準値)の基準クロックを複数必要とするPHY、スイッチ、ASIC、FPGAに隣接して配置するように設計されています。

最大27個の設定をオンチップOTP(ワンタイムプログラマブル)メモリまたは外部I2C EEPROMに保存可能です。 複数のクロックソースからの冗長入力に対応し、リファレンスクロックのバックアップ用途として利用可能です。