特長

- 6 - 0.7 V current mode differential output pairs (HCSL)

- CLKREQ# pin for outputs 1 and 4/ supports Express Card applications

- PLL or bypass mode/PLL can dejitter incoming clock

- Selectable PLL bandwidth/minimizes jitter peaking in downstream PLL's

- Spread Spectrum Compatible/tracks spreading input clock for low EMI

- SMBus Interface/unused outputs can be disabled

- Cycle-to-cycle jitter < 50 ps

- Output-to-output skew < 50 ps

説明

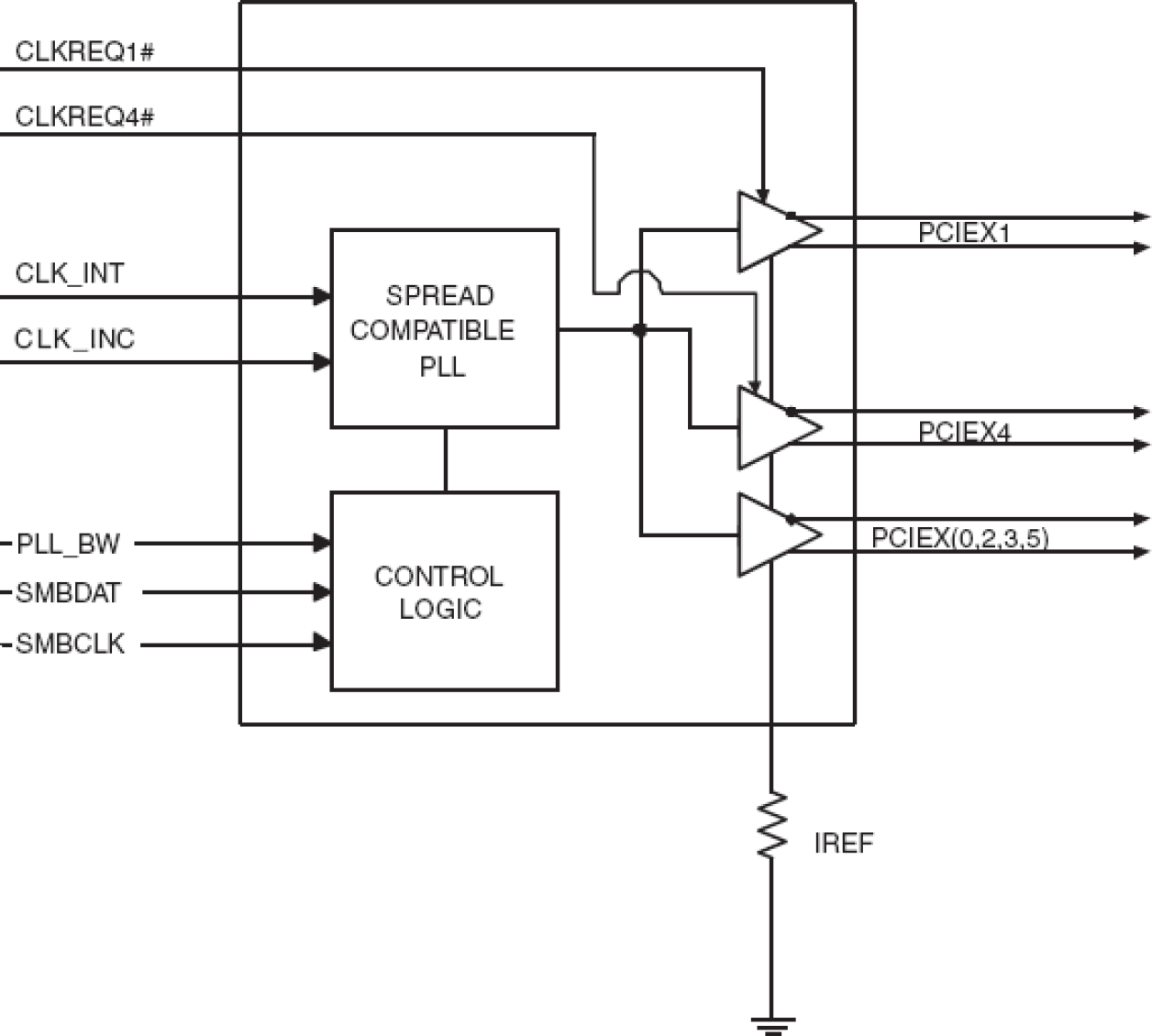

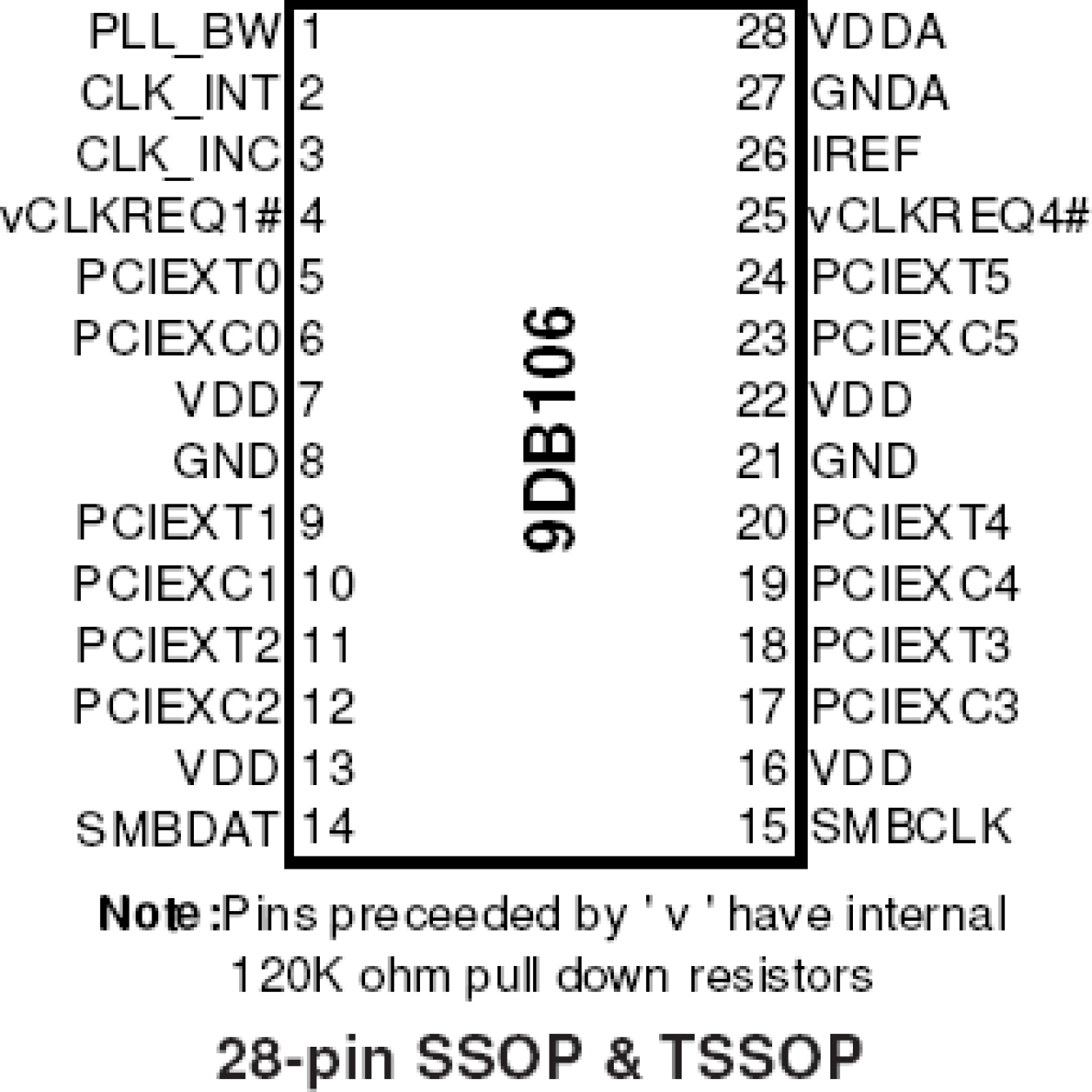

The 9DB106 zero-delay buffer supports PCIe Gen1 and Gen2 clocking requirements. The 9DB106 is driven by a differential SRC output pair from an IDT CK410/CK505-compliant main clock generator. It attenuates jitter on the input clock and has a selectable PLL bandwidth to maximize performance in systems with or without Spread-Spectrum clocking. An SMBus interface allows control of the PLL bandwidth and bypass options, while 2 clock request (CLKREQ#) pins make the 9DB106 suitable for Express Card applications.

パラメータ

| 属性 | 値 |

|---|---|

| Diff. Outputs | 6 |

| Diff. Output Signaling | HCSL |

| Output Freq Range (MHz) | 80 - 105 |

| Diff. Inputs | 1 |

| Diff. Input Signaling | HCSL |

| Accepts Spread Spec Input | Yes |

| Power Consumption Typ (mW) | 429 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Output Type | HCSL |

| Diff. Termination Resistors | 24 |

| Package Area (mm²) | 42.7 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 100 - 100 |

| Function | Zero Delay Buffer |

| Input Type | HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 3.3 |

パッケージオプション

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TSSOP | 9.7 x 4.4 x 1.0 | 28 | 0.65 |

適用されたフィルター

フィルター

ソフトウェア/ツール

サンプルコード

シミュレーションモデル

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

In this episode, Ron Wade from IDT (acquired by Renesas) explains PCIe common clocking and its impact on timing solutions. Learn about using a single clock source, fan-out buffers, and the considerations for spread spectrum and non-spread spectrum clocking in PCIe systems.

In this video, we explore PCIe with separate reference clocks and the effects of clock selection. Learn how separate reference clocks work and their impact on system performance and stability.

This video provides a high-level overview of Separate Reference Clock with Independent Spread (SRIS) architectures for PCI Express systems, additional performance requirements that this clocking architecture imposes on the reference clocks, and some system implications encountered trying to implement the architecture.