パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | CABGA |

| Pkg. Code: | AJG144 |

| Lead Count (#): | 144 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.2 |

| Pitch (mm): | 0.8 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 144 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 1500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e1 SnAgCu |

| Temp. Range (°C) | -40 to 85°C |

| Application | PTP Timing Card, SETS, Low-cTE Timing Card |

| Channels (#) | 8 |

| Clock Support | G.813, G.8262, G.8262.1, GR-1244-CORE, GR-253-CORE, G.8273.2 |

| Core Voltage (V) | 2.5V, 3.3V |

| Diff. Inputs | 8 |

| Diff. Outputs | 12 |

| Family Name | ClockMatrix |

| Fractional Output Dividers (#) | 8 |

| Function | System Synchronizer |

| Input Freq (MHz) | 5.0E-7 - 1000 |

| Input Type | HCSL, LVDS, LVHSTL, LVPECL, SSTL |

| Inputs (#) | 16 |

| Length (mm) | 10 |

| Loop Bandwidth Range (Hz) | 9.0E-5 - 12000 |

| MOQ | 1500 |

| Output Banks (#) | 8 |

| Output Freq Range (MHz) | 5.0E-7 - 1000 |

| Output Skew (ps) | 50 |

| Output Type | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL |

| Output Voltage (V) | 1.2V, 1.5V, 1.8V, 2.5V, 3.3V |

| Outputs (#) | 24 |

| Phase Jitter Max RMS (ps) | 0.2 |

| Phase Jitter Typ RMS (ps) | 0.15 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.2 |

| Pkg. Type | CABGA |

| Product Category | IEEE 1588 |

| Prog. Interface | I2C, SPI |

| Reel Size (in) | 13 |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | Yes |

| Thickness (mm) | 1.2 |

| Width (mm) | 10 |

| Xtal Freq (KHz) | 25 - 54 |

| 掲載 | No |

8A34001 に関するリソース

説明

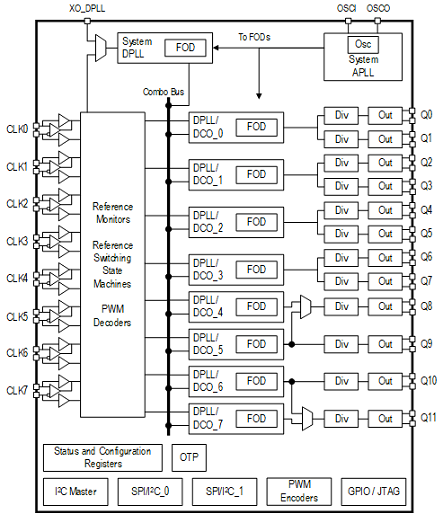

8A34001 IEEE 1588対応システムシンクロナイザは、IEEE 1588 高精度時間プロトコル(PTP)と同期イーサネット(SyncE)に基づいて超低ジッタの高精度タイミング信号を生成します。 システムのタイミング・同期ソースとして1台で使用することも、システムの信頼性向上のために2台で冗長ペアとして使用することも可能です。 デジタル制御オシレータ(DCO)は、外部プロセッサで動作するIEEE1588クロックリカバリサーボソフトウェアで制御することが可能です。 SyncEの同期装置タイミング ソース(SETS)の実装に必要なデジタルPLL(DPLL)や、その他タイミングブロックにより、物理層のタイミングをサポートしています。 DCOは、IEEE1588の情報だけで制御することも、ITU-T G.8273.2に準拠した状態で、IEEE1588の時刻情報とSyncEからの物理層周波数情報を組み合わせて制御することも可能です。 このデバイスは、バックプレーン間や回路基板間のクロック伝搬遅延を積極的に測定・補正し、システム内のIEEE 1588タイムスタンプユニット(TSU)間で時間誤差を最小限に抑えた正確な時刻と位相を確実に配信するために使用することが可能です。 このデバイスは、IEEE 1588クロック合成、SyncEクロック生成、ジッタ減衰、ユニバーサル周波数変換を制御する複数の独立チャネルをサポートしています。 入力から入力、入力から出力、出力から出力の位相スキューをすべて正確に管理できます。 最大28GbpsのSERDESやCPRI/OBSAI、SONET/SDH、PDHインタフェースおよび、IEEE1588 TSUを直接同期できる超低ジッタクロックを出力します。

この製品ファミリの他のデバイスについては、ClockMatrixタイミングソリューションのページをご覧ください。 IEEE 1588システムでの同期を容易に実現するために、ルネサスはPTPクロックマネージャソフトウェアをライセンスに基づき無償で提供しています。