特長

- Programmable frequency synthesis optimized for instrumentation, networking and computing applications

- 81MHz to 2592MHz synthesized clock output signal

- Two differential, universal LVDS or LVPECL compatible high-frequency outputs

- Output frequency programmable through 2-wire I2C bus or parallel interface

- On-chip crystal oscillator for reference frequency generation

- Alternative LVCMOS/LVTTL compatible reference clock input

- Clock stop and output enable functionality

- PLL lock indicator output (LVCMOS/LVTTL)

- LVCMOS/LVTTL compatible control inputs

- Fully integrated PLL

- SiGe Technology

- Full 3.3V supply voltage

- -40°C to 85°C ambient operating temperature

- Available in a lead-free (RoHS 6) compliant package

説明

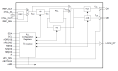

The 844S42I is a 3.3V compatible, PLL based clock synthesizer targeted for clock generation in high-performance instrumentation, networking and computing applications. Using either the serial (I2C) or parallel programming interface, the 844S42I enables the generation of clock frequencies in the range of 81MHz to 2592MHz. The internal crystal oscillator uses the external quartz crystal as the basis of its frequency reference. Alternatively, a LVCMOS compatible clock signal can be used as PLL reference signal. The devices uses an integer-N synthesizer architecture and is optimized for low-jitter generation. The VCO within the PLL operates over a range of 1296MHz to 2592MHz. Its output is scaled by a divider that is configured by either the I2C or parallel interfaces. The crystal oscillator frequency fXTAL, the PLL pre-divider P, the feedback-divider M and the PLL post-divider N determine the output frequency. The feedback path of the PLL is internal. The PLL post-dividers NA and NB are configured through either the I2C or the parallel interfaces, each can provide one of seven division ratios (1, 2, 3, 4, 6, 8, 16). This divider extends the performance of the part while providing a typical 50% duty cycle. The high-frequency outputs QA and QB are differential and are capable of driving a pair of transmission lines. The positive supply voltage for the internal PLL is separated from the power supply for the core logic and output drivers to minimize noise induced jitter. The serial interface is I2C compatible and provides read and write access to the internal PLL configuration registers. The lock state of the PLL is indicated by the LVCMOS-compatible LOCK_DT output. This device provides a clock enable control input that, when active (LOW), allows the outputs to switch normally, and when inactive (HIGH), places the outputs in a high impedance state. The 844S42I is packaged in a 8mm x 8mm 56-lead VFQFN package.

適用されたフィルター