特長

- Clock frequencies up to 100 MHz (6.5 ns access time)

- Clocked FIFO buffering data from Port A to Port B

- Programmable Almost-Empty and Almost-Full flags

- Serial or parallel programming of partial flags

- Port B bus sizing of 36 bits (long word), 18 bits (word) and 9 bits (byte)

- Big- or Little-Endian format for word and byte bus sizes

- Mailbox bypass registers for each FIFO

- Free-running CLKA and CLKB may be asynchronous or coincident

- Available in 128-pin TQFP package

- Pin compatible with the lower density parts 72V36x3

- Industrial temperature range (–40C to +85C) is available

説明

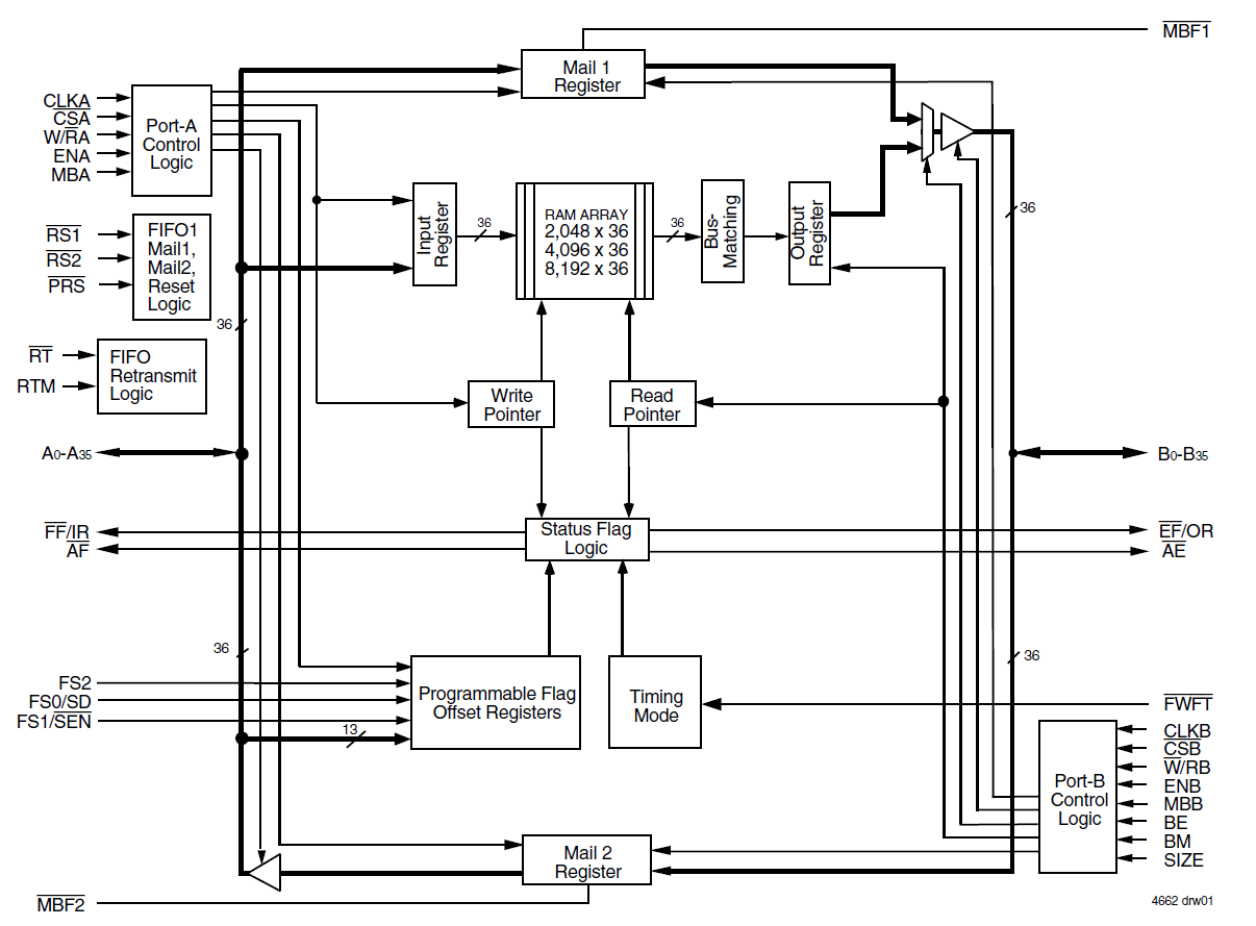

The 72V3663 is a 4K x 36 Sync FIFO that is a 3.3V version of the 723663. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses with synchronous control. Communication between each port may bypass the FIFO via two mailbox registers. The FIFO has Retransmit capability which resets the read pointer to the first memory location. This device can operate in IDT Standard mode or First Word Fall Through mode.

適用されたフィルター