特長

- Std., A, and C speeds

- Low input and output leakage <1 uA (max.)

- CMOS power levels

- True TTL input and output compatibility:– VOH = 3.3V (typ.)

- – VOL = 0.3V (typ.)

- High Drive outputs (-15mA IOH, 48mA IOL)

- Meets or exceeds JEDEC standard 18 specifications

- Military product compliant to MIL-STD-883, Class B and DESC listed (dual marked)

- Power off disable outputs permit "live insertion"

- Available in 20 pin CERDIP and LCC package

説明

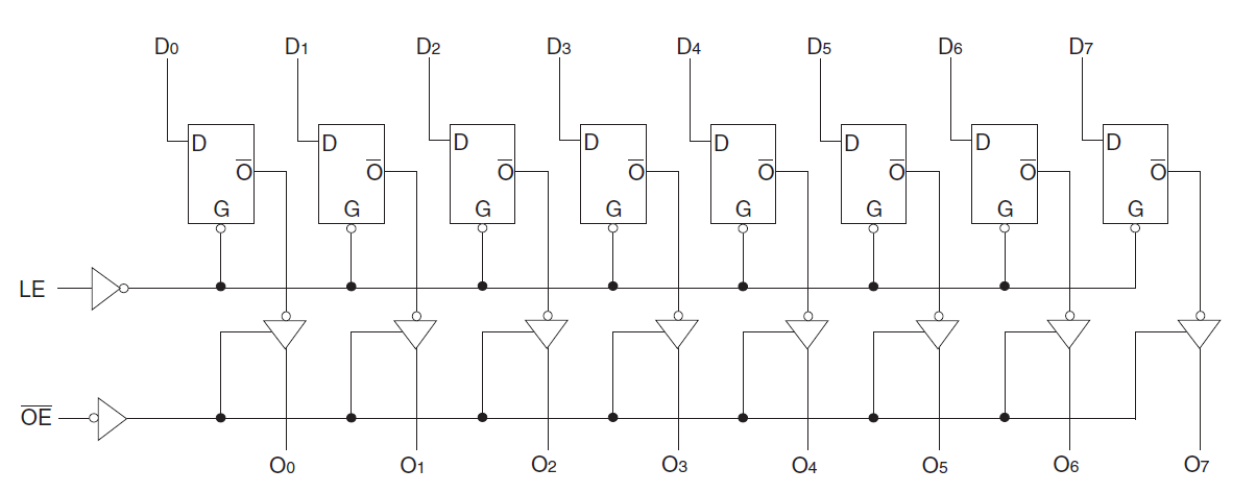

The IDT 54FCT573T is an octal transparent latch with 3-state outputs and is intended for bus oriented applications. The flip-flops appear transparent to the data when Latch Enable (LE) is high. When LE is low, the data that meets the set-up time is latched. The 54FCT573T operates at -55C to +125C. (For commercial version, see 74FCT573T)

適用されたフィルター