Features

- Six LVCMOS / LVTTL outputs

- Outputs able to drive 12 series terminated lines

- Crystal Oscillator Interface

- Crystal input frequency range: 10MHz to 40MHz

- Output skew: 80ps (maximum)

- RMS phase jitter @ 25MHz, (100Hz – 1MHz): 0.26ps (typical), VDD = VDDO = 2.5V

Offset Noise Power

100Hz.................-129.7 dBc/Hz

1kHz...................-144.4 dBc/Hz

10kHz.................-147.3 dBc/Hz

100kHz...............-157.3 dBc/Hz - 5V tolerant enable inputs

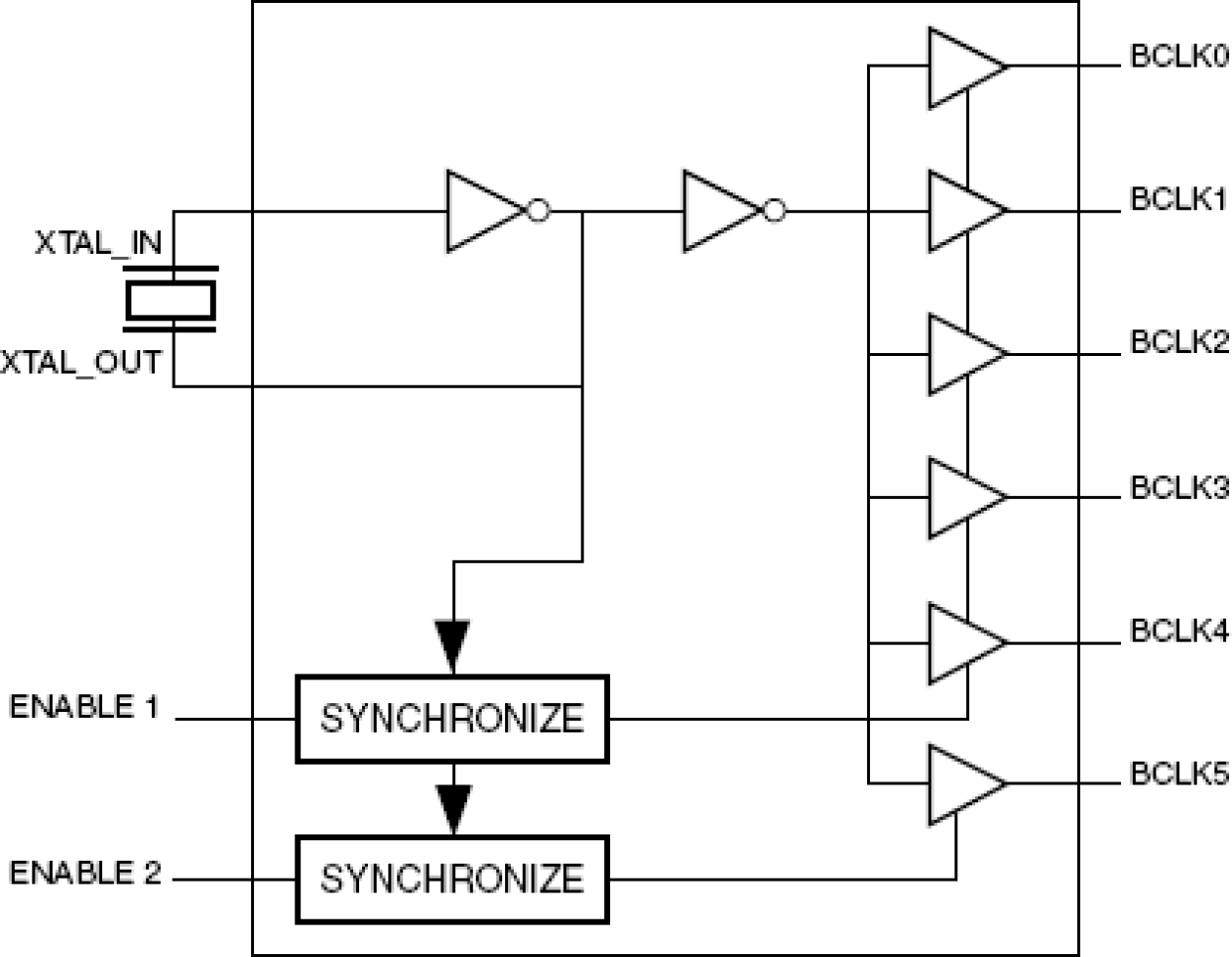

- Synchronous output enables

- Operating power supply modes:

Full 3.3V, 2.5V, 1.8V

Mixed 3.3V core/2.5V output operating supply

Mixed 3.3V core/1.8V output operating supply

Mixed 2.5V core/1.8V output operating supply - 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Description

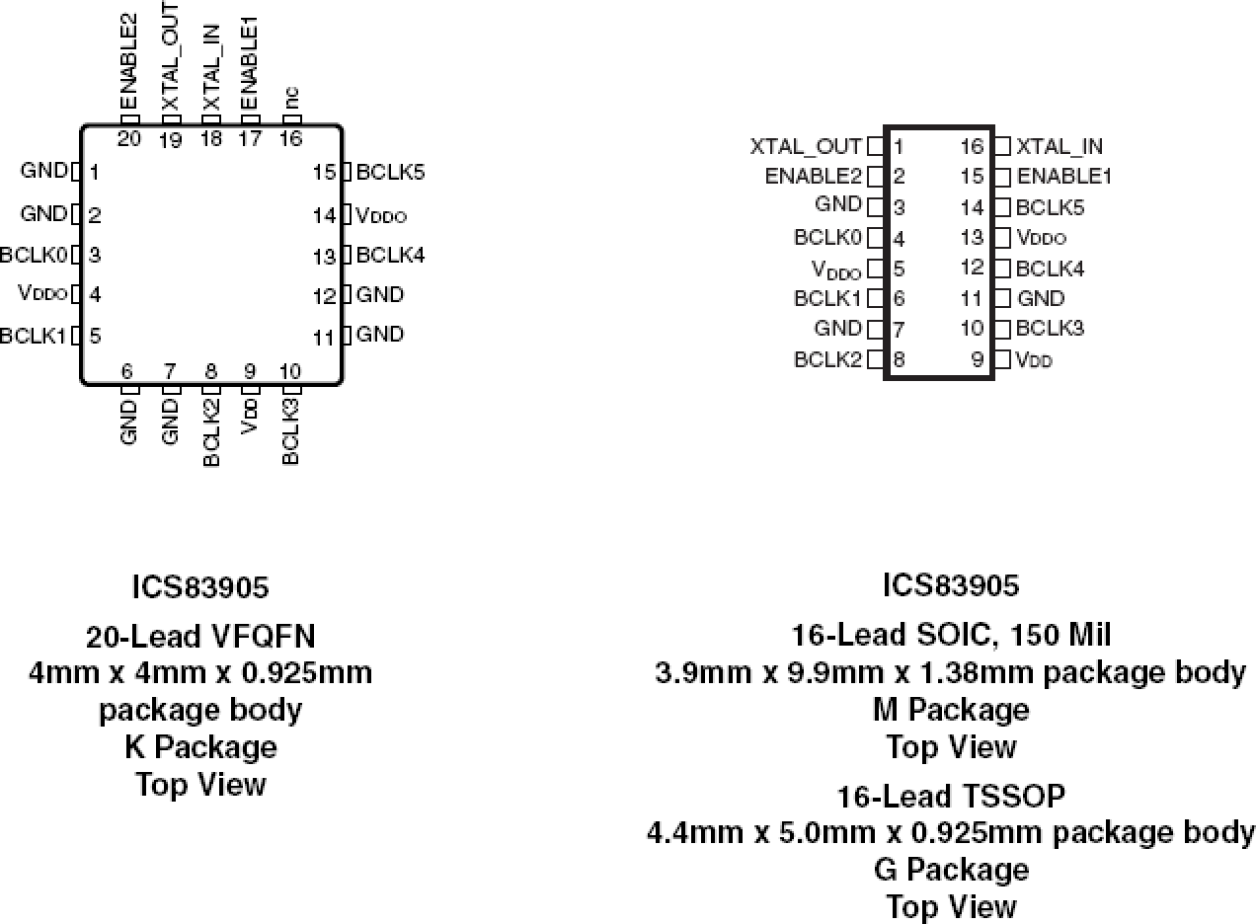

The 83905 is a low skew, 1-to-6 LVCMOS / LVTTL Fanout Buffer. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The effective fanout can be increased from 6 to 12 by utilizing the ability of the outputs to drive two series terminated lines. The 83905 is characterized at full 3.3V, 2.5V, and 1.8V, mixed 3.3V/2.5V, 3.3V/1.8V and 2.5V/1.8V output operating supply mode. Guaranteed output and part-to-part skew characteristics along with the 1.8V output capabilities makes the 83905 ideal for high performance, single ended applications that also require a limited output voltage.

Applied Filters: