Features

- Typical tSK(o) (output skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015

- > 200V using machine model (C = 200pF, R = 0)

- VCC = 3.3V ± 0.3V, normal range

- VCC = 2.7V to 3.6V, extended range

- CMOS power levels (0.4µW typ. static)

- All inputs, outputs, and I/O are 5V tolerant

- Available in a 48-pin TSSOP package

Description

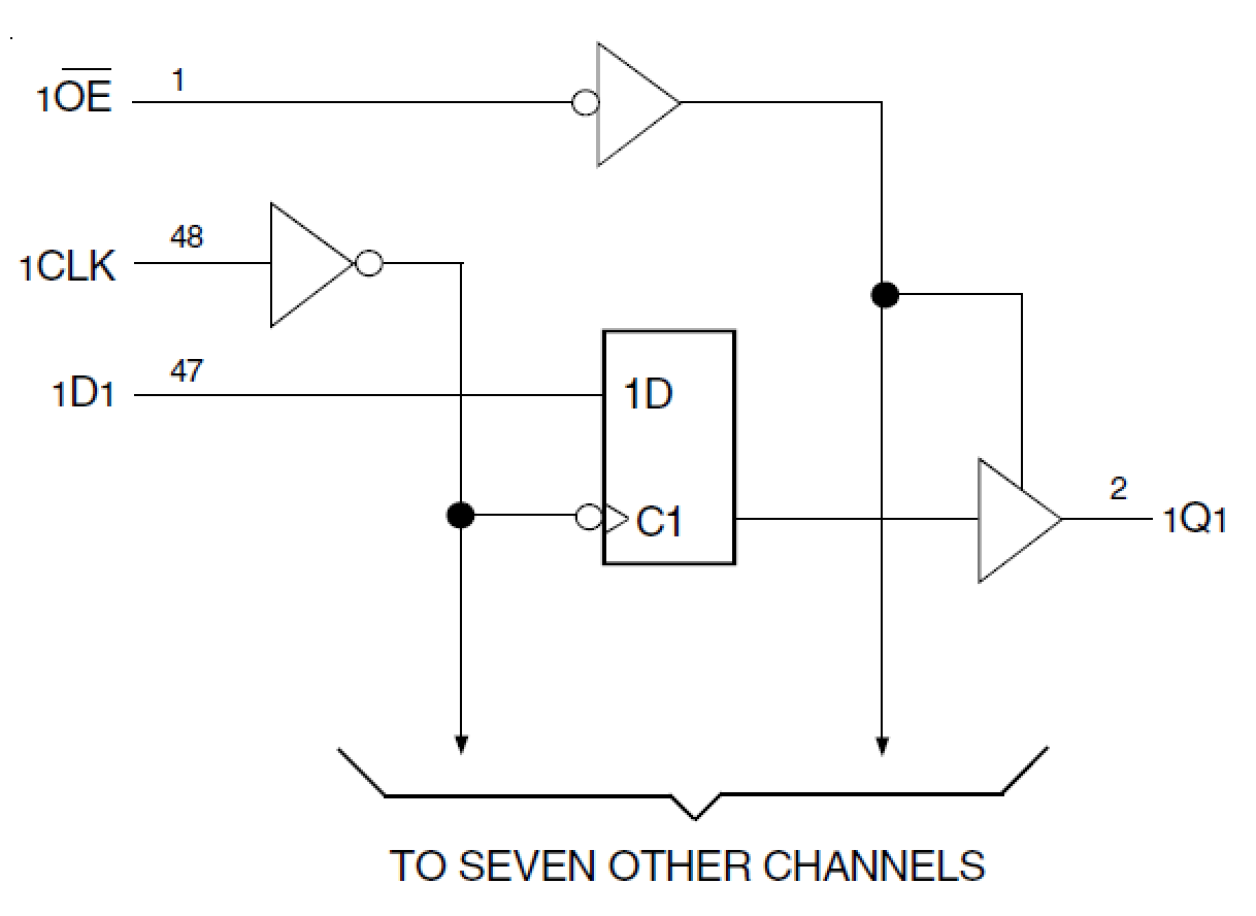

The 74LVCH162374A 16-bit high-speed, low-power edge-triggered D-type flip-flop is ideal for use as a buffer register for data synchronization and storage. It can operate as two 8-bit registers or one 16-bit register with a common clock. All pins of the 74LVCH162374A can be driven from either 3.3V or 5V devices which allows the use of this device as a translator in a mixed 3.3V/5V supply system. The 74LVCH162374A has "bus-hold" which prevents floating inputs and eliminates the need for pull-up/down resistors. The 74LVCH162374A operates at -40 °C to +85 °C.

Parameters

| Attributes | Value |

|---|---|

| Function | Flip-flop |

| Pkg. Code | PAG48 |

| Temp. Range (°C) | -40 to 85°C |

| Bus Width (bits) | 16 |

| Core Voltage (V) | 3.3 |

| Output Type | 3-state |

| Speed Grade | A |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TSSOP | 12.5 x 6.1 x 1.0 | 48 | 0.5 |

Applied Filters: