Features

- 10ns read/write cycle time

- 5V input tolerant

- Renesas Standard or First Word Fall Through timing

- Single or double register-buffered Empty and Full flags

- Easily expandable in depth and width

- Asynchronous or coincident Read and Write Clocks

- Asynchronous or synchronous programmable Almost-Empty and Almost-Full flags with default settings

- Half-Full flag capability

- Output enable puts output data bus in high-impedance state

- Available in 64-pin TQFP and STQFP packages

- Industrial temperature range (–40°C to +85°C) is available

Description

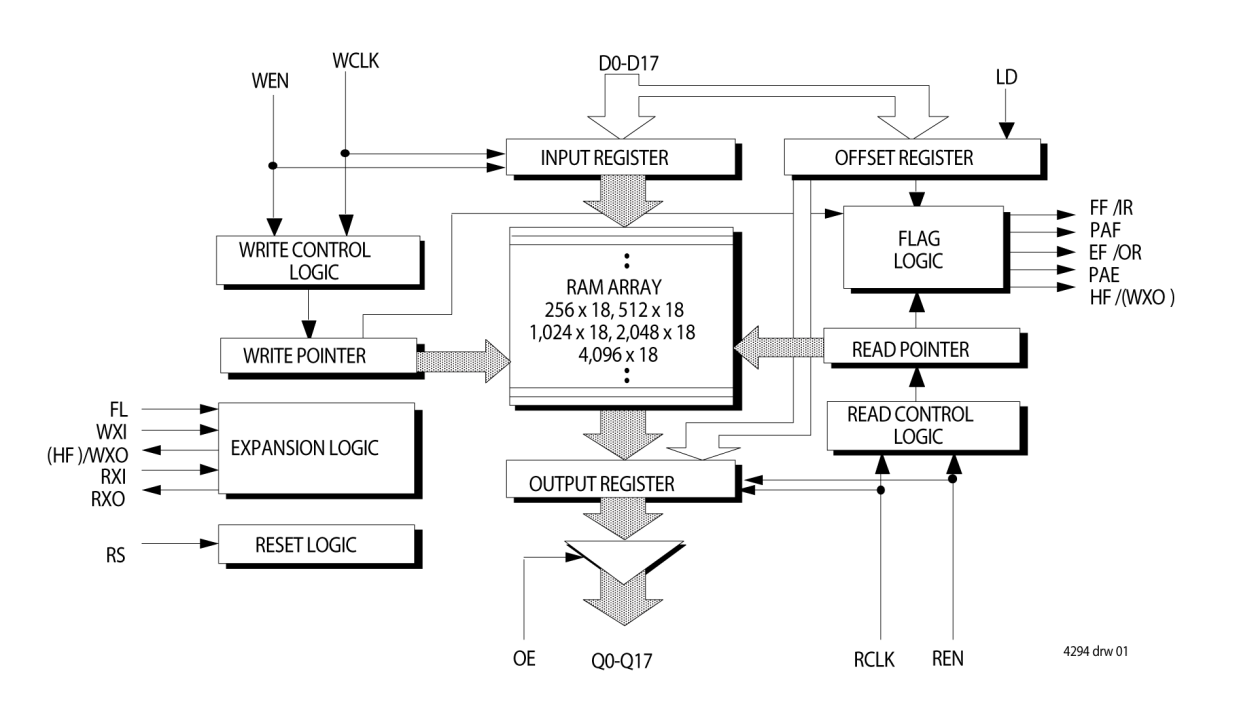

The 72V245 is a 4K x 18 first-in, first-out (FIFO) memory with clocked read and write controls. It is a 3.3V version of the 72245 FIFO and is applicable for a wide variety of data buffering needs, such as optical disk controllers, Local Area Networks (LANs), and interprocessor communication. It has 18-bit input and output ports. The Read Clock (RCLK) can be tied to the Write Clock for single-clock operation, or the two clocks can run asynchronously of one another for dual-clock operation.

Parameters

| Attributes | Value |

|---|---|

| Core Voltage (V) | 3.3 |

| Bus Width (bits) | 18 |

| Density (Kb) | 72 |

| Pkg. Code | PNG64, PPG64 |

| Interface | Synchronous |

| I/O Type | 3.3 V LVTTL |

| I/O Frequency (MHz) | 66 - 66, 100 - 100 |

| Organization | 4K x 18 |

| Temp. Range (°C) | -40 to 85°C, 0 to 70°C |

| Architecture | Uni-directional |

Applied Filters: