Overview

Description

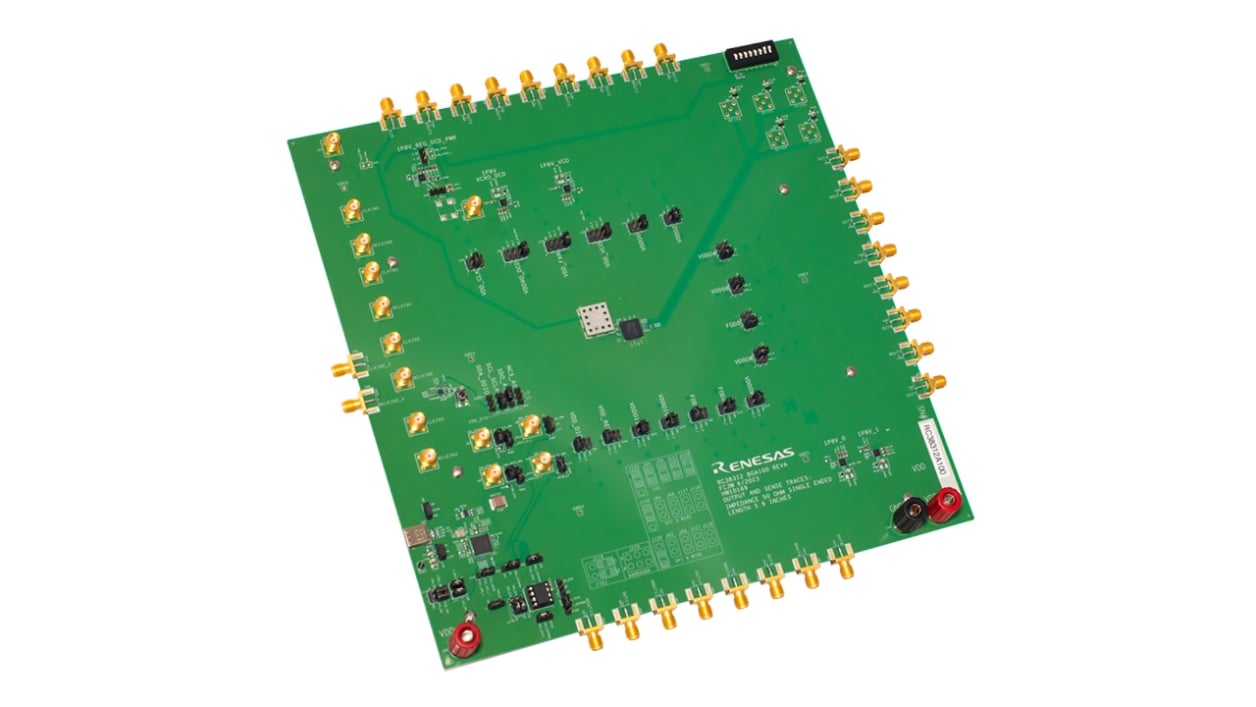

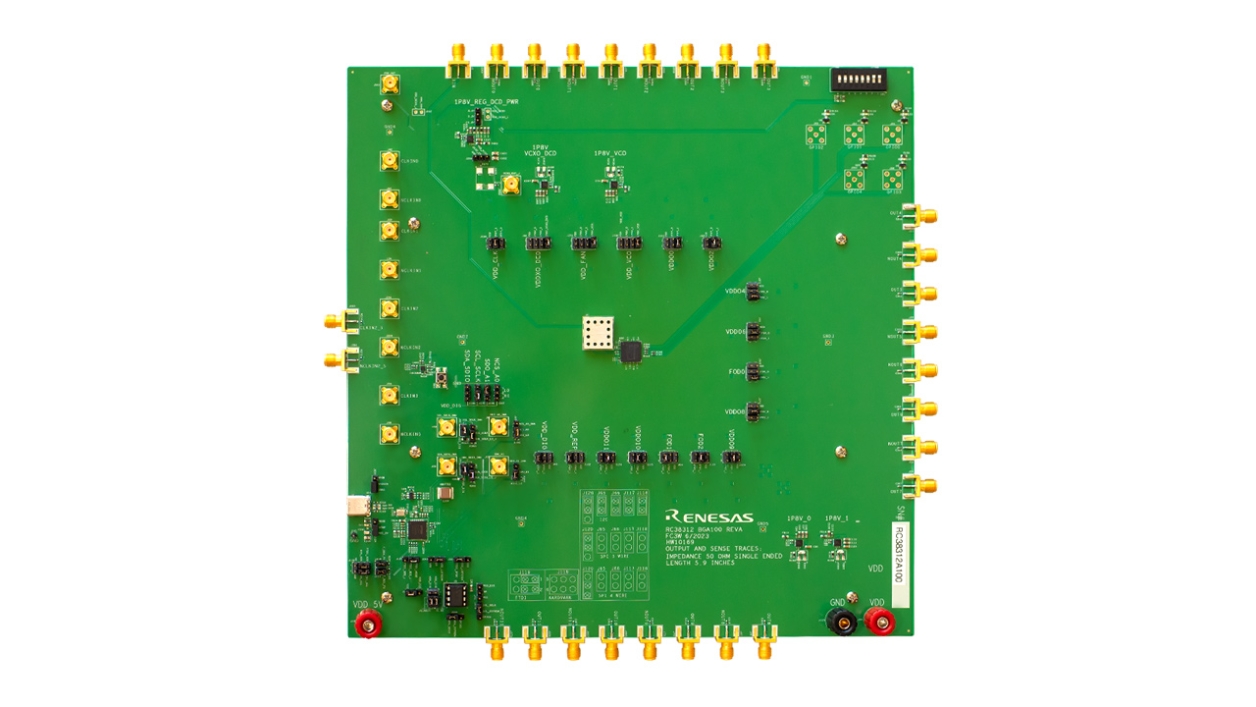

This RC38312A evaluation kit is used to evaluate the RC38312 FemtoClock™ 3 ultra-low phase noise radio synchronizer, multi-frequency clock synthesizer. The RC38312/RC38112 is an ultra-low phase noise radio synchronizer, multi-frequency clock synthesizer, and digitally controlled oscillator (DCO). This flexible, low-power device outputs clocks with ultra-low in-band phase noise and spurious signals for 4G and 5G RF transceivers and with jitter below 18fs RMS for 112Gbps and 224Gbps SerDes.

Features

- Four differential clock inputs

- Twelve differential clock outputs

- Onboard EEPROM stores startup configuration data

- XIN terminal can use a laboratory signal generator or OCXO/TCXO/XO components and board

- Laboratory power supply connectors

- Serial port for configuration and register readout

Applications

Design & Development

Videos & Training

Learn about the FemtoClock 3 Wireless ultra-low phase noise synchronizer and jitter attenuator for 5G radio units, distribution units, and high-performance precision timing protocol.

News & Blog Posts

Blog Post Oct 8, 2024 |

Support

Support Communities

Get quick technical support online from Renesas Engineering Community technical staff.

Knowledge Base

Browse our knowledge base for helpful articles, FAQs, and other useful resources.