Features

- Six LVPECL outputs

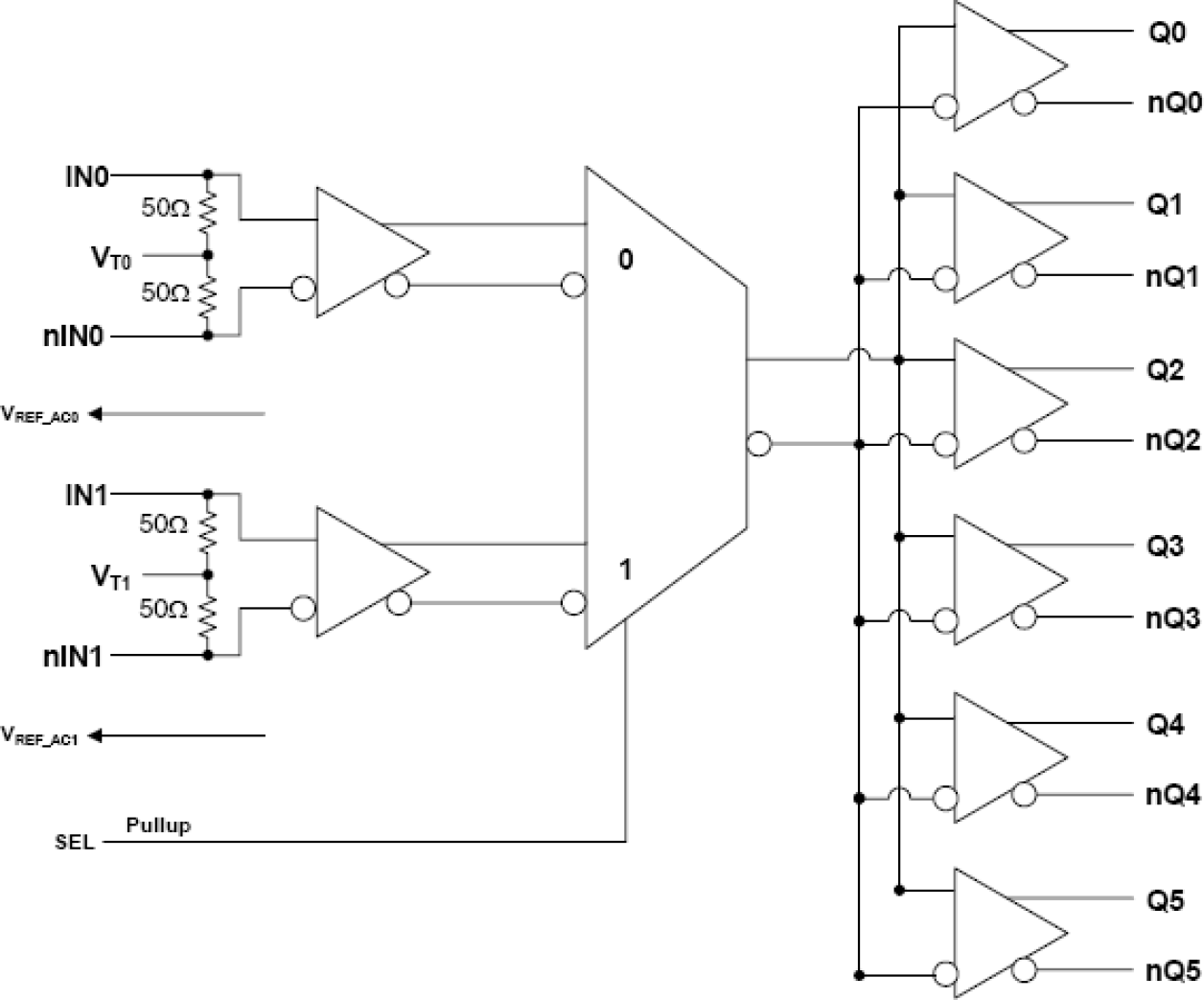

- INx, nINx inputs can accept the following differential input levels: LVPECL, LVDS, CML

- 50Ω internal input termination to VT

- Two selectable differential input pairs

- Maximum output frequency: 3.2GHz

- Output Skew: 45ps (maximum)

- Part-to-part skew: 200ps (maximum)

- Additive phase jitter, RMS: 47fs (typical), (fREF = 622.08MHz, 12kHz to 20MHz, VCC = 3.3V)

- Propagation Delay: 580ps (maximum)

- LVPECL mode operating voltage supply range: VCC = 2.5V±5%, 3.3V±10%, VEE = 0V

- -40 °C to 85 °C ambient operating temperature

Description

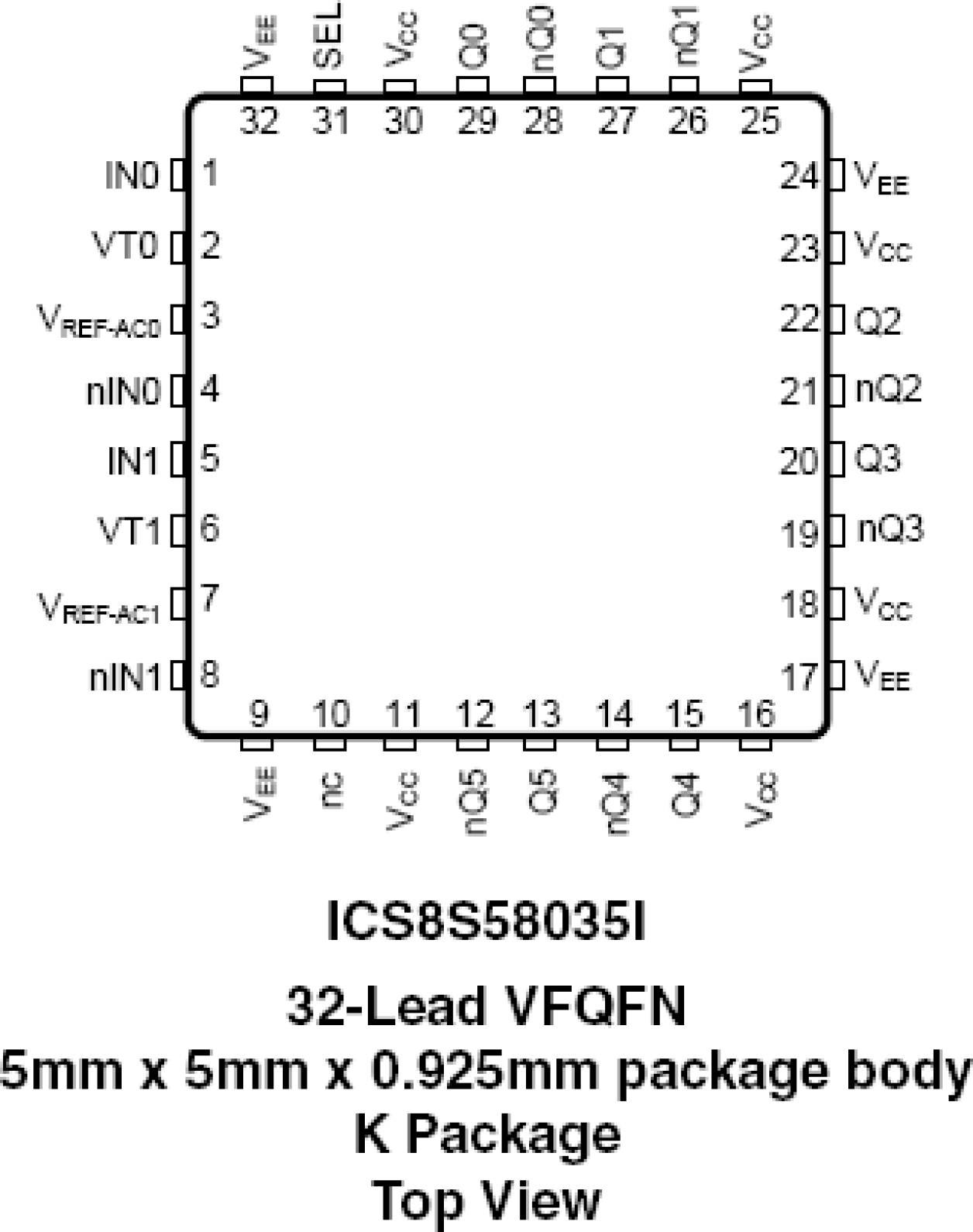

The 8S58035I is a high-speed 2-to-6 Differential-to-LVPECL fanout buffer. The 8S58035I is optimized for high-speed and very low output skew, making it suitable for use in demanding applications such as SONET, 1 Gigabit and 10 Gigabit Ethernet, and Fiber Channel. The internally terminated differential inputs and VREF_AC pins allow other differential signal families such as LVDS, LVDS, and CML to be easily interfaced to the input with minimal use of external components. The device also has a 2:1 MUX input, allowing for easy selection between two clock reference sources. The 8S58035I is packaged in a small 5mm x 5mm 32-pin VFQFN package which makes it ideal for use in space-constrained applications.

Parameters

| Attributes | Value |

|---|---|

| Output Freq Range (MHz) | 3200 |

| Supply Voltage (V) | 2.5 - 2.5, 3.3 - 3.3 |

| Output Type | LVPECL |

| Package Area (mm²) | 25 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 2 |

| Input Freq (MHz) | 3200 |

| Adjustable Phase | No |

| Channels (#) | 1 |

| Additive Phase Jitter Typ RMS (fs) | 47 |

| Function | Buffer, Multiplexer |

| Input Type | CML, LVDS, LVPECL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 2.5V, 3.3V |

| Output Voltage (V) | 2.5V, 3.3V |

| Product Category | Clock Buffers & Drivers, Clock Multiplexers, RF Buffers |

Package Options

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 5.0 x 5.0 x 0.9 | 32 | 0.5 |

Applied Filters: