特長

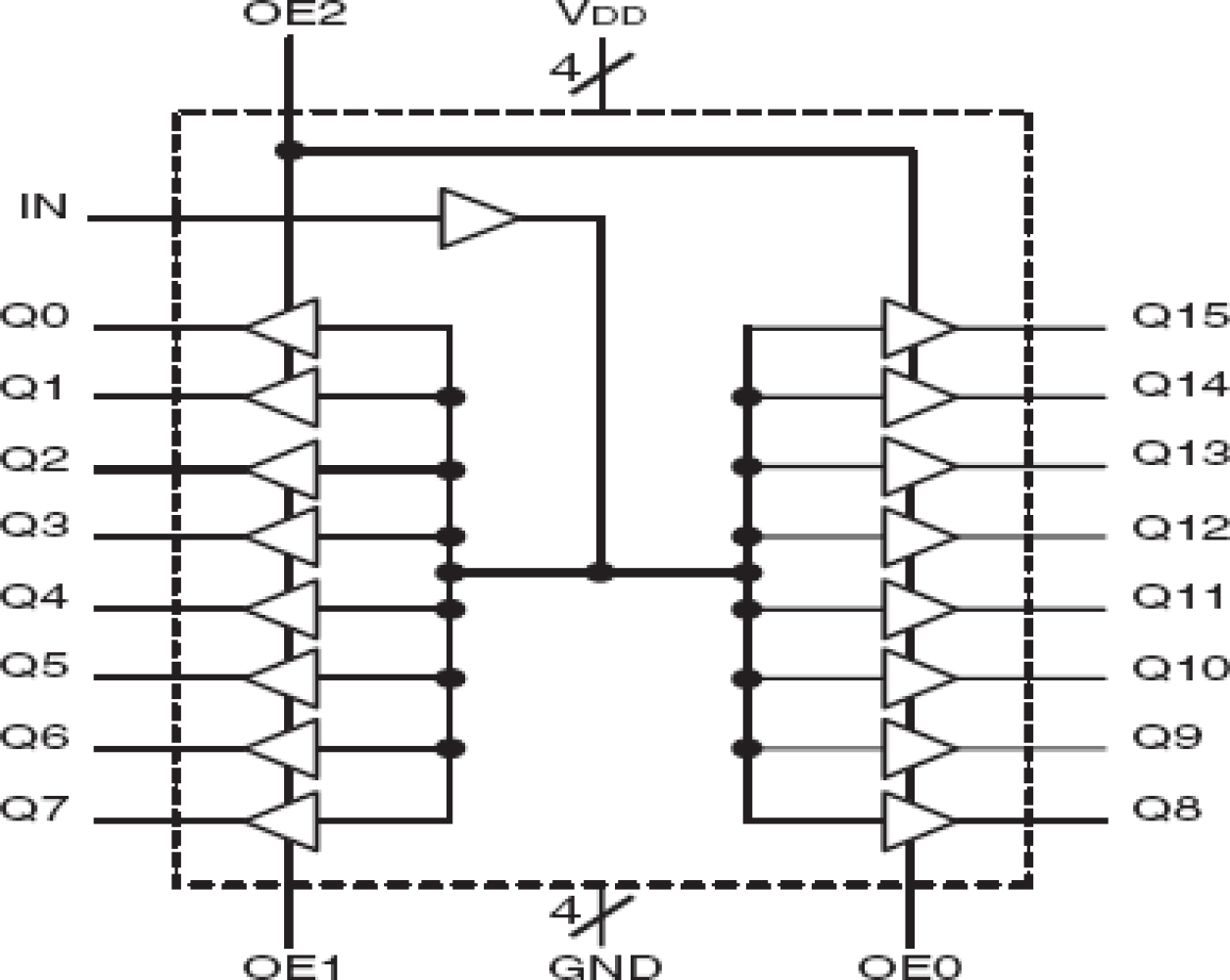

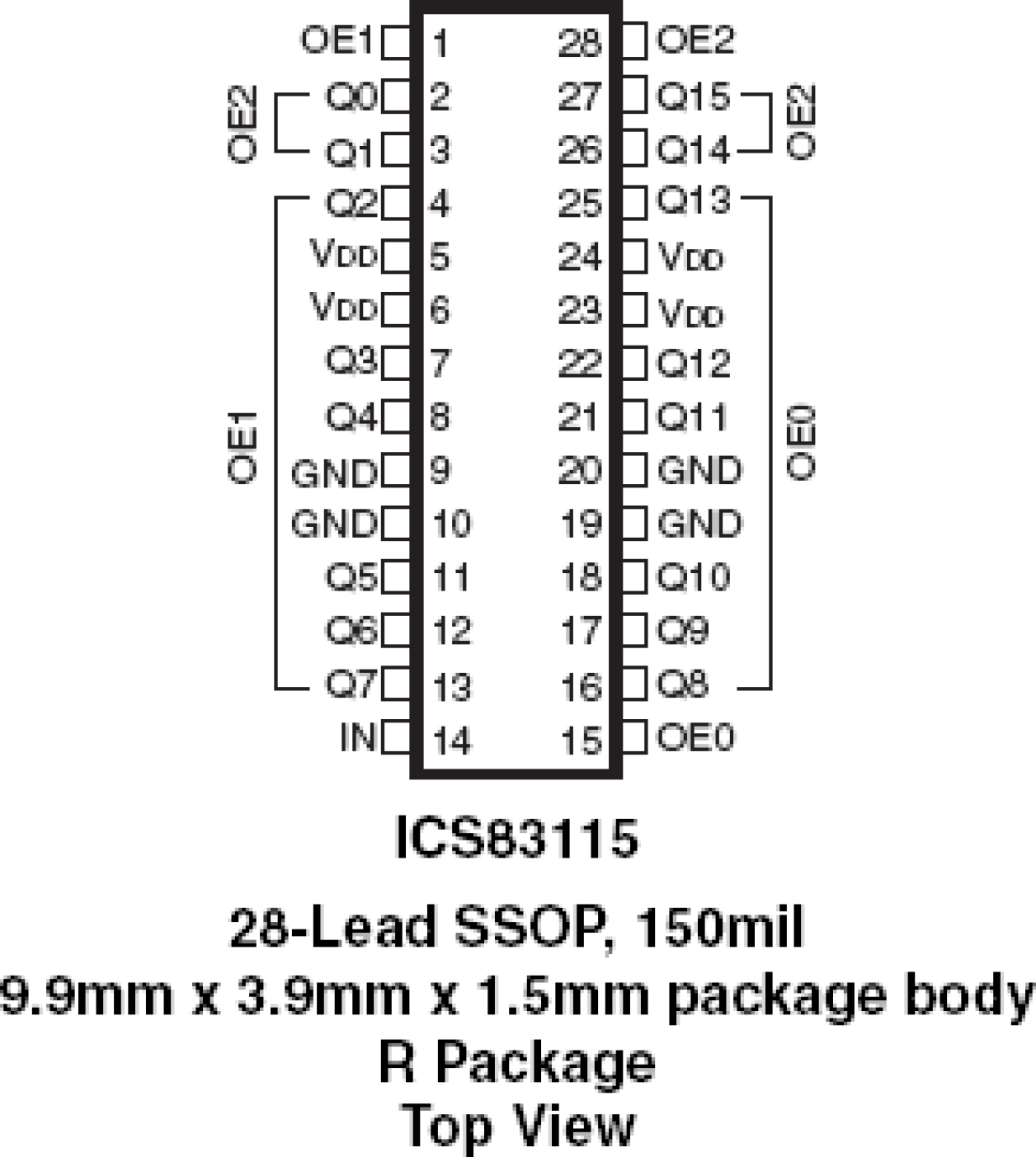

- Sixteen LVCMOS / LVTTL outputs, 15Ω output impedance

- One LVCMOS / LVTTL clock input

- Maximum output frequency: 200MHz

- All inputs are 5V tolerant

- Output skew: 250ps (maximum)

- Part-to-part skew: 800ps (maximum)

- Additive phase jitter, RMS: 0.09ps (typical)

- Full 3.3V operating supply

- 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

説明

The 83115 is a low skew, 1-to-16 LVCMOS/ LVTTL Fanout Buffer. The 83115 single-ended clock input accepts LVCMOS or LVTTL input levels. The 83115 operates at full 3.3V supply mode over the commercial temperature range. Guaranteed output and part-to-part skew characteristics make the 83115 ideal for those clock distribution applications demanding well defined performance and repeatability.

適用されたフィルター