特長

- 8.0MHz Operating Frequency (5962-9052502)

- 2.0MHz Operating Frequency (HD3-6402R)

- Low Power CMOS Design

- Programmable Word Length, Stop Bits and Parity

- Automatic Data Formatting and Status Generation

- Compatible with Industry Standard UARTs

- Single +5V Power Supply

- CMOS/TTL Compatible Inputs

- Pb-Free Plus Anneal Available (RoHS Compliant)

説明

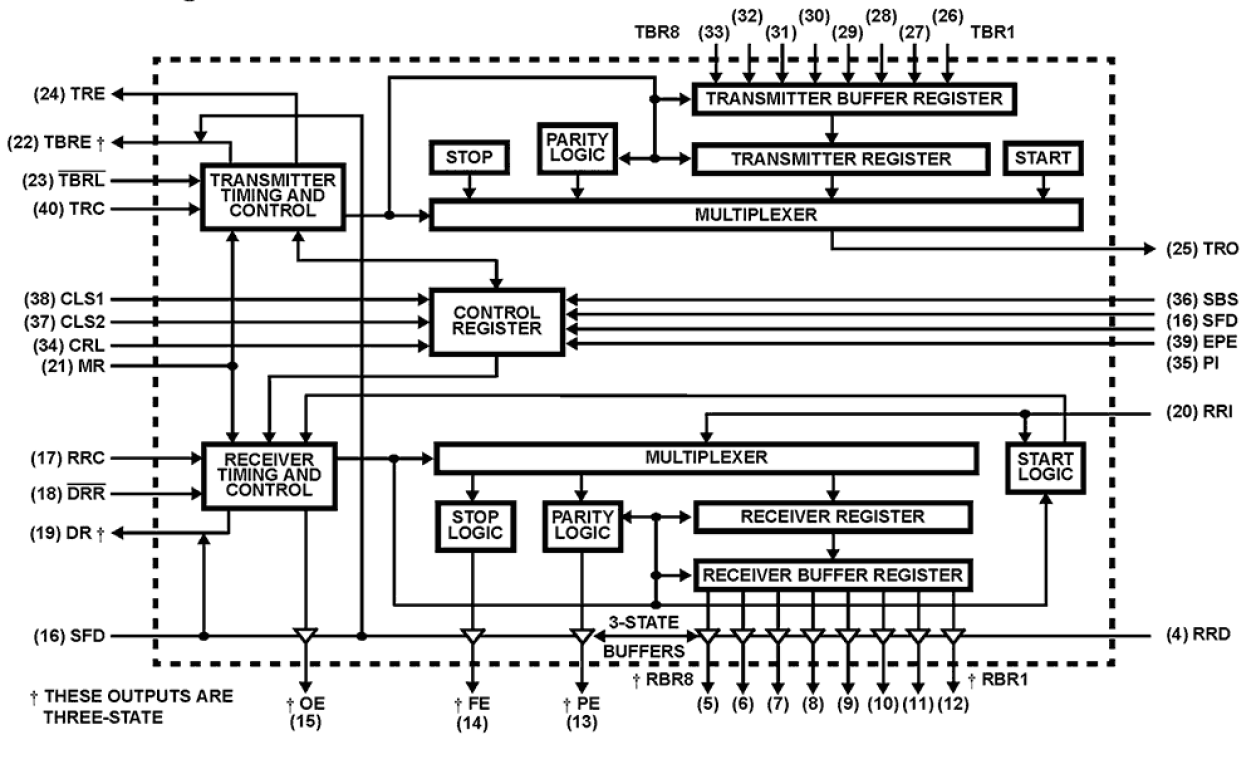

The HD-6402 is a CMOS UART for interfacing computers or microprocessors to an asynchronous serial data channel. The receiver converts serial start, data, parity and stop bits. The transmitter converts parallel data into serial form and automatically adds start, parity and stop bits. The data word length can be 5, 6, 7 or 8 bits. Parity may be odd or even. Parity checking and generation can be inhibited. The stop bits may be one or two or one and one-half when transmitting 5-bit code. The HD-6402 can be used in a wide range of applications including modems, printers, peripherals and remote data acquisition systems. Utilizing the Intersil advanced scaled SAJI IV CMOS process permits operation clock frequencies up to 8. 0MHz (500K Baud). Power requirements, by comparison, are reduced from 300mW to 10mW. Status logic increases flexibility and simplifies the user interface.

適用されたフィルター