特長

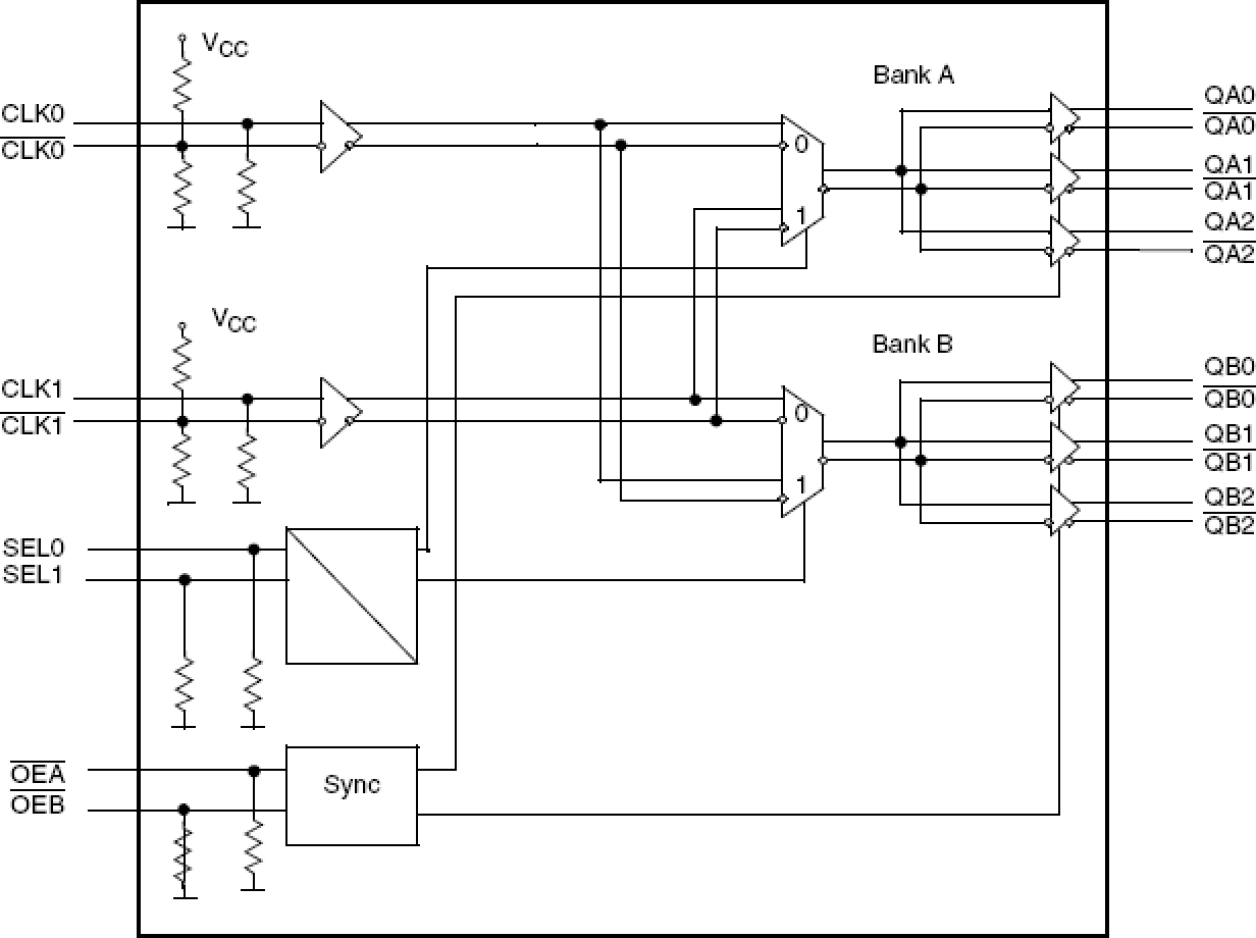

- Fully differential architecture from input to all outputs

- SiGe technology supports near-zero output skew

- Supports DC to 3 GHz operation(1) of clock or data signals

- LVPECL compatible differential clock inputs and outputs

- LVCMOS compatible control inputs

- Single 3.3 V or 2.5 V supply

- 50 ps maximum device skew(1)

- Synchronous output enable eliminating output runt pulse generation and metastability

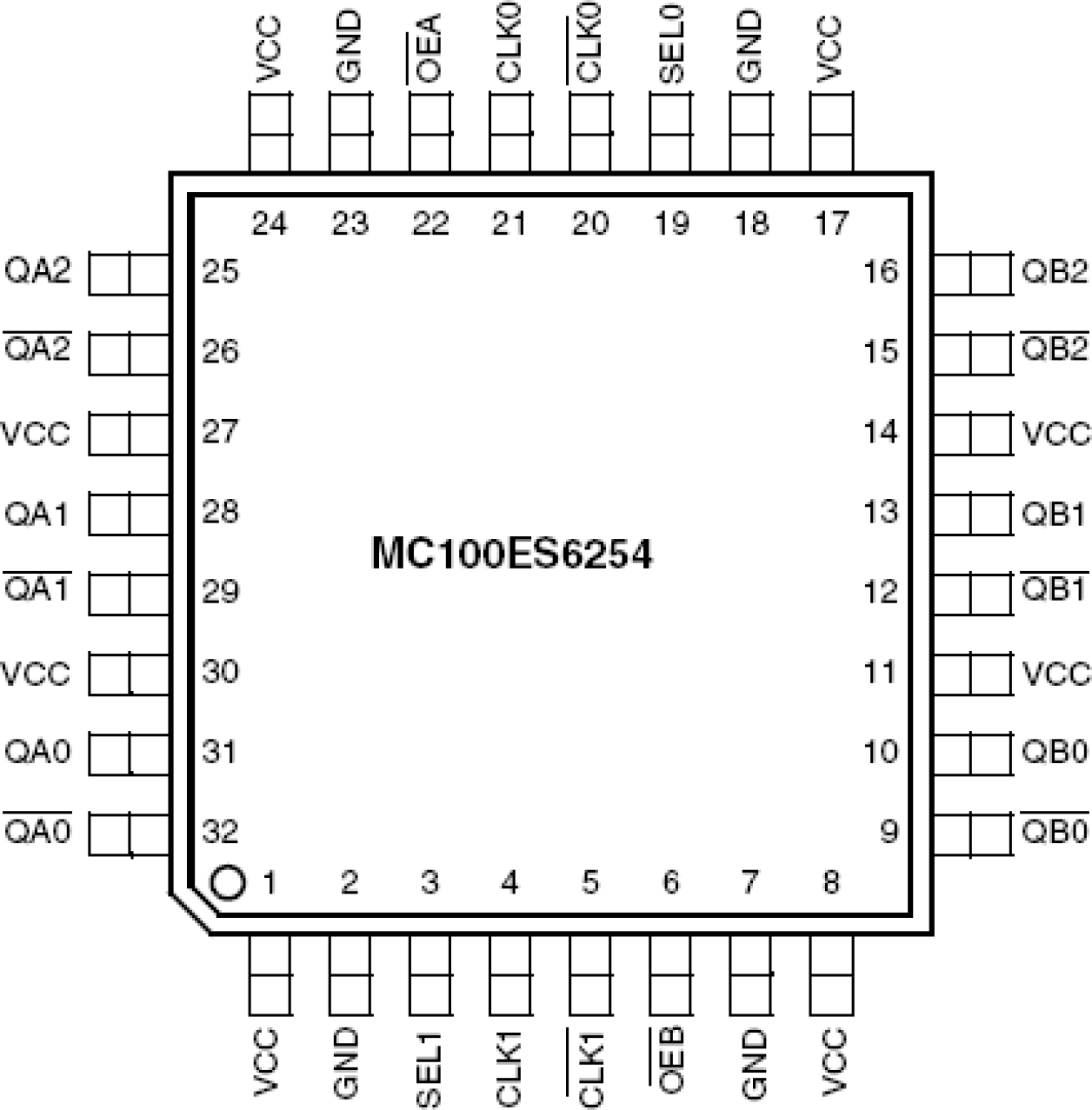

- Standard 32 lead LQFP package

- Industrial temperature range

- 32-lead Pb-free package available

説明

MC100ES6254 is designed for very skew critical differential clock distribution systems and supports clock frequencies from DC up to 3.0 GHz. Typical applications for the MC100ES6254 are primary clock distribution, switching and loopback systems of high-performance computer, networking and telecommunication systems, as well as on-board clocking of OC-3, OC-12 and OC-48 speed communication systems. Primary purpose of the MC100ES6254 is high-speed clock switching applications. In addition, the MC100ES6254 can be configured as single 1:6 or dual 1:3 LVPECL fanout buffer for clock signals, or as loopback device in high-speed data applications. The MC100ES6254 can be operated from a 3.3 V or 2.5 V positive supply without the requirement of a negative supply line.

適用されたフィルター