パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | SSOP |

| Pkg. Code: | PYG28 |

| Lead Count (#): | 28 |

| Pkg. Dimensions (mm): | 10.2 x 5.3 x 1.73 |

| Pitch (mm): | 0.65 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 28 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 1500 |

| Qty. per Carrier (#) | 0 |

| Package Area (mm²) | 54.1 |

| Pkg. Dimensions (mm) | 10.2 x 5.3 x 1.73 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Advanced Features | Spread Spectrum |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2 |

| C-C Jitter Max P-P (ps) | 25 |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 90 - 140 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 1 |

| Length (mm) | 10.2 |

| MOQ | 1500 |

| Output Banks (#) | 6 |

| Output Freq Range (MHz) | 90 - 140 |

| Output Skew (ps) | 100 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 6 |

| Phase Jitter Typ RMS (ps) | 3 |

| Pitch (mm) | 0.65 |

| Pkg. Type | SSOP |

| Product Category | PCI Express Clocks |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | Yes |

| Thickness (mm) | 1.73 |

| Width (mm) | 5.3 |

9DB306 に関するリソース

説明

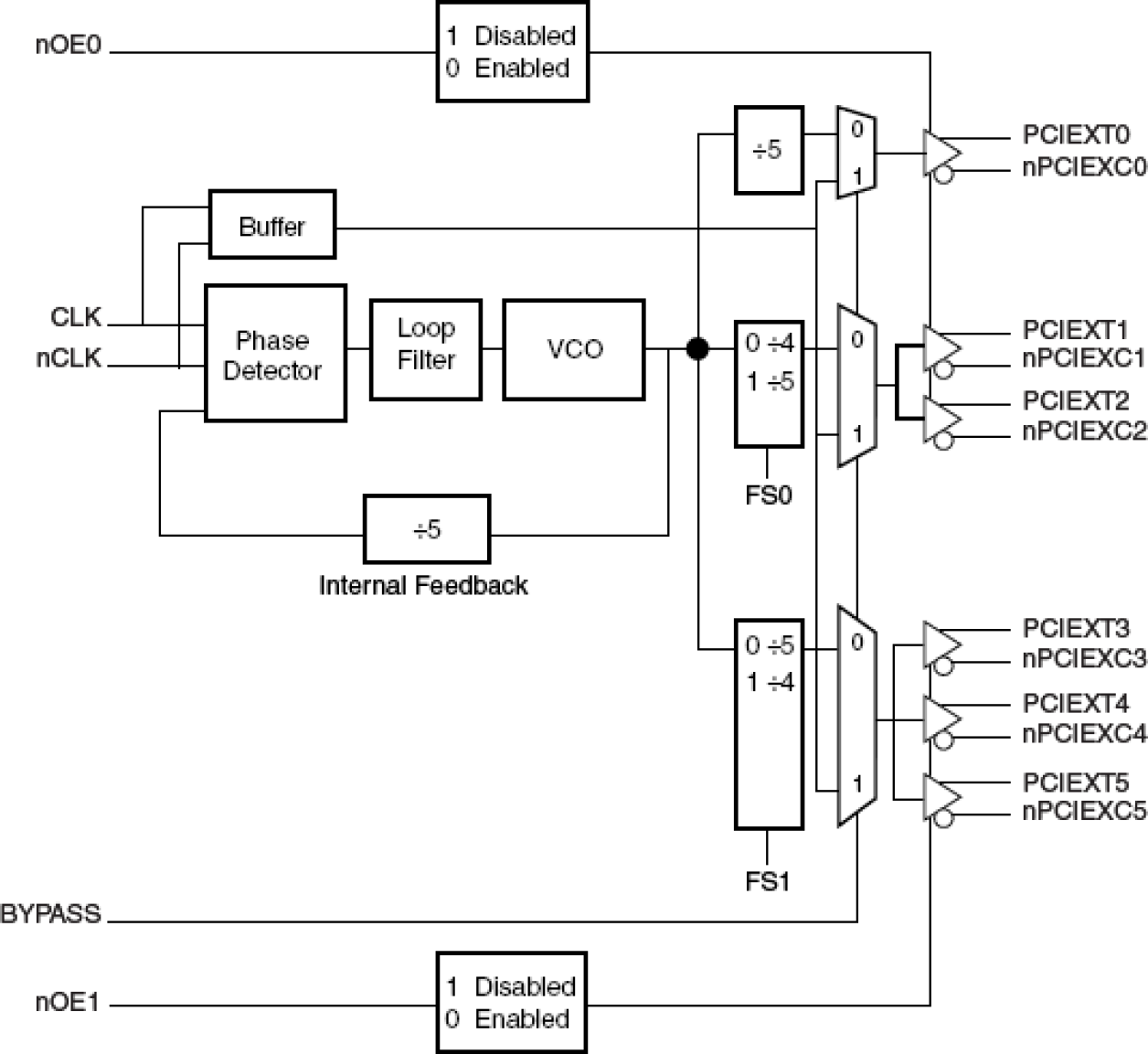

The 9DB306 is a high performance 1-to-6 Differential-to- LVPECL Jitter Attenuator designed for use in PCI Express systems. In some PCI Express systems, such as those found in desktop PCs, the PCI Express clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a zero delay buffer may be required to attenuate high frequency random and deterministic jitter components from the PLL synthesizer and from the system board. The 9DB306 has 2 PLL bandwidth modes. In low bandwidth mode, the PLL loop BW is about 500kHz and this setting will attenuate much of the jitter from the reference clock input while being high enough to pass a triangular input spread spectrum profile. There is also a high bandwidth mode which sets the PLL bandwidth at 1MHz which will pass more spread spectrum modulation. For SerDes which have x30 reference multipliers instead of x25 multipliers, 5 of the 6 PCI Express outputs (PCIEX1:5) can be set for 125MHz instead of 100MHz by configuring the appropriate frequency select pins (FS0:1). Output PCIEX0 will always run at the reference clock frequency (usually 100MHz) in desktop PC PCI Express Applications.