特長

- Four banks of two low-skew outputs

- Selectable bank output divider values: ÷1 through ÷6 and ÷8

- One differential PCLK, nPCLK input

- PCLK, nPCLK input pair can accept the following differential input levels: LVPECL, LVDS, or CML

- Maximum input frequency: 1.5GHz

- LVCMOS control inputs

- QXx ÷1 edge aligned to QXx ÷n edge

- Individual output divider control via serial interface

- Individual output enable/disable control via serial interface

- Individual output type control, LVDS or LVPECL, via serial interface

- 2.375V to 3.465V supply voltage operation

- -40 °C to 85 °C ambient operating temperature

- Lead-free (RoHS 6) packaging

- Supported by Renesas' Timing Commander™ software

説明

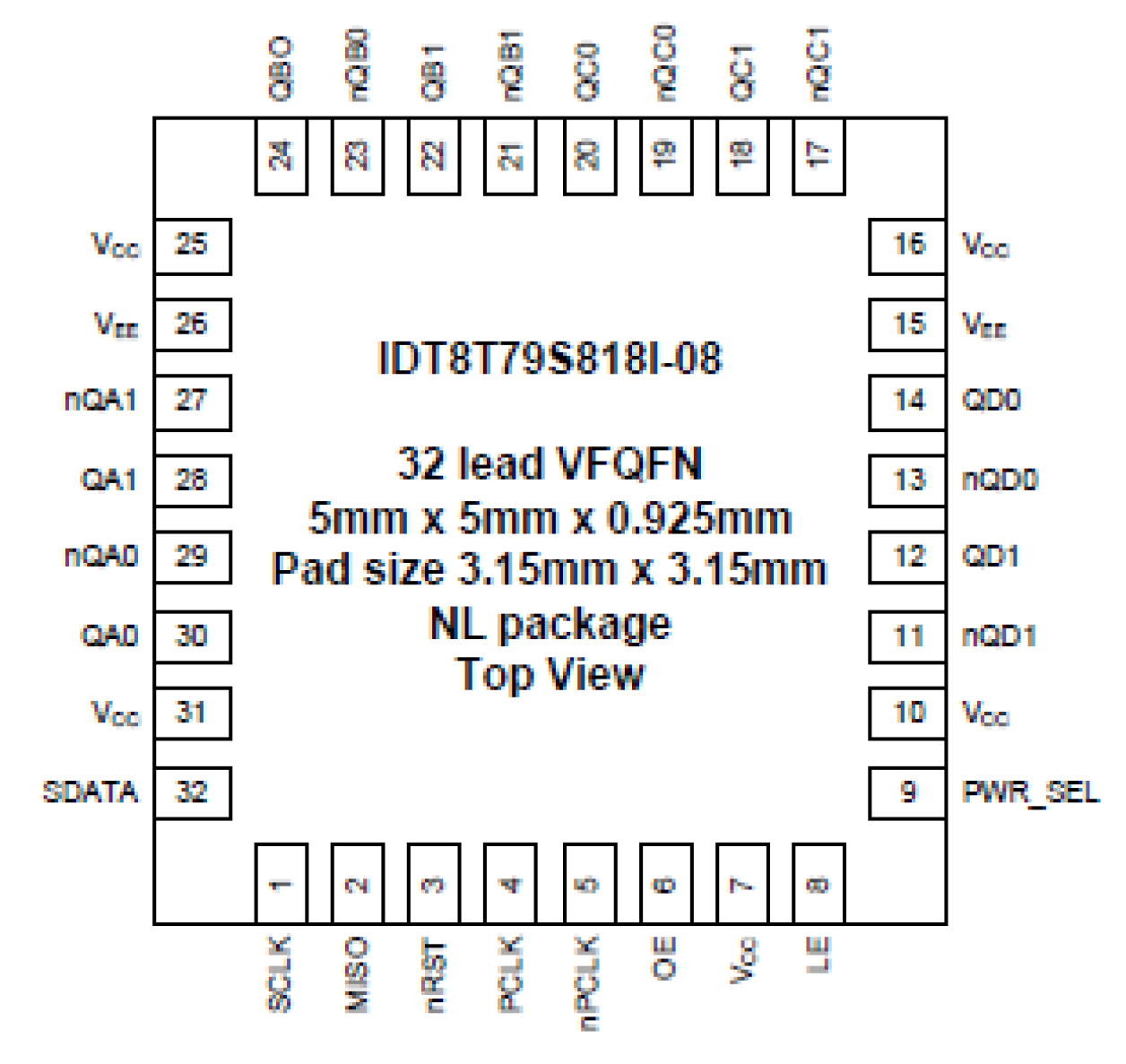

The 8T79S818I-08 is a high-performance, 1-to-8, differential input to universal output clock divider and fanout buffer. The device is designed for frequency division and signal fanout of high-frequency clock signals in applications requiring four different output frequencies generated simultaneously. Each bank of two outputs has a selectable divider value of ÷1 through ÷6 and ÷8. The 8T79S818I-08 is optimized for 3.3V and 2.5V supply voltages and a temperature range of -40 °C to 85 °C. The device is packaged in a space-saving 32-lead VFQFN package.

適用されたフィルター