特長

- Clock generation of: 62.5MHz, 125MHz, 156.25MHz, and 312.5MHz

- Two banks of two differential CML clock outputs

- Crystal interface designed for 25MHz, 12pF parallel resonant crystal

- RMS phase jitter at 125MHz, using a 25MHz crystal (1.875MHz to 20MHz): 0.486ps (typical)

- Offset single-side band phase noise

- 100Hz: -97 dBc/Hz

- 1kHz: -118 dBc/Hz

- 10kHz: -125 dBc/Hz

- 100kHz: -123 dBc/Hz

- LVCMOS interface levels for the control inputs

- Full 3.3V and 2.5V supply voltage

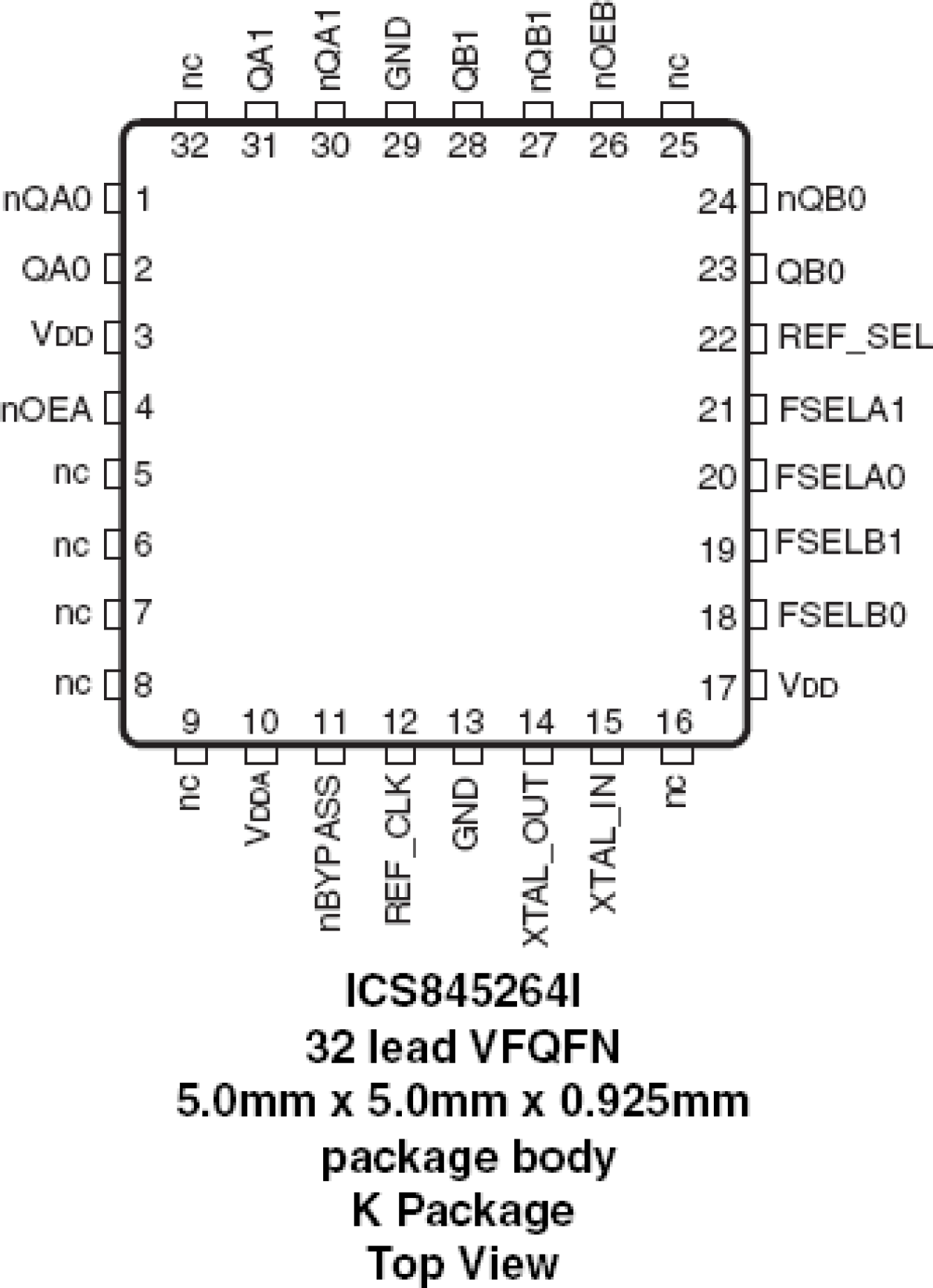

- Lead-free (RoHS 6) 32-lead VFQFN packaging

- -40 °C to 85 °C ambient operating temperature

説明

The ICS845264I is a 3.3V, 2.5V CML clock generator designed for Ethernet applications. The device synthesizes four clock frequencies on two separately selectable output banks. Each bank has either a 62.5MHz, 125MHz, 156.25MHz, or 312.5MHz clock signal with excellent phase jitter performance. Each clock frequency is distributed to two low-skew differential CML output banks with a total of four outputs. The device is suitable for driving the reference clocks of Ethernet PHYs. It supports 3.3V and 2.5V voltage supply and is packaged in a small, lead-free (RoHS 6) 32-lead VFQFN package. The extended temperature range supports telecommunication, wireless infrastructure, and networking end equipment requirements.

適用されたフィルター