特長

- A and C speeds

- Typical tSK(o) (Output Skew) 250ps

- ESD > 2000V per MIL-STD-883, Method 3015

- > 200V usingmachine model (C = 200pF, R = 0)

- VCC = 3.3V ± 0.3V, Normal Range, or VCC = 2.7V to 3.6V, ExtendedRange

- CMOS power levels (0.4 uW typ. static)

- Rail-to-rail output swing for increased noise margin

- Low Ground Bounce (0.3V typ.)

- Inputs (except I/O) can be driven by 3.3V or 5V components

- Available in 56 pin TSSOP package

説明

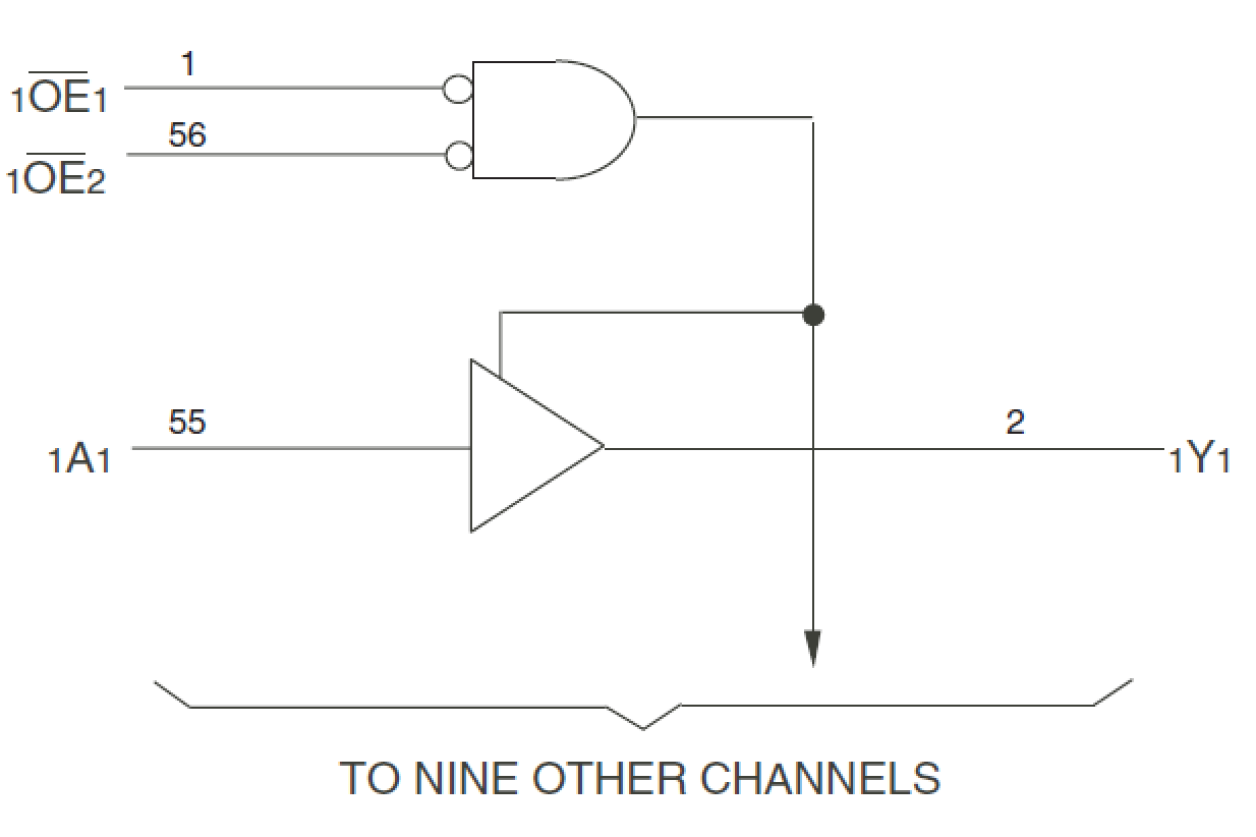

The 74FCT163827 20-bit buffer provide high-performance bus interface buffering for wide data/address paths or busses carrying parity. The 74FCT163827 has series current limiting resistors reducing the need for external series terminating resistors. The inputs of the 74FCT163827 can be driven from either 3.3V or 5V devices. This feature allows the use of these devices as translators in a mixed 3.3V/5V supply system. The 74FCT163827 operates at -40C to +85C

適用されたフィルター