特長

- Dynamic Port B bus sizing of 36 bits (long word), 18 bits (word), and 9 bits (byte)

- Selection of Big- or Little-Endian format for word and byte bus sizes

- Three modes of byte-order swapping on Port B

- Programmable Almost-Full and Almost-Empty flags

- Microprocessor interface control logic

- FF , AF flags synchronized by CLKA

- EF , AE flags synchronized by CLKB

- Passive parity checking on each Port

- Parity Generation can be selected for each Port

- Available in 132-pin PQFP and 120-pin TQFP packages

- Industrial temperature range (–40C to +85C) is available

説明

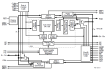

The 72V3613 is a 64 x 36 3.3V Sync FIFO which supports clock frequencies up to 83 MHz and has read-access times as fast as 8 ns. Three modes of byte-order swapping are possible with any bus-size selection. Communication between each port can bypass the FIFO via two 36-bit mailbox registers. The continuous clocks for each port are independent of one another and can be asynchronous or coincident.

適用されたフィルター