特長

- 4 – 0.7V current mode differential HCSL output pairs

- Low additive jitter

- suitable for use in PCIe Gen2 and Gen3 systems

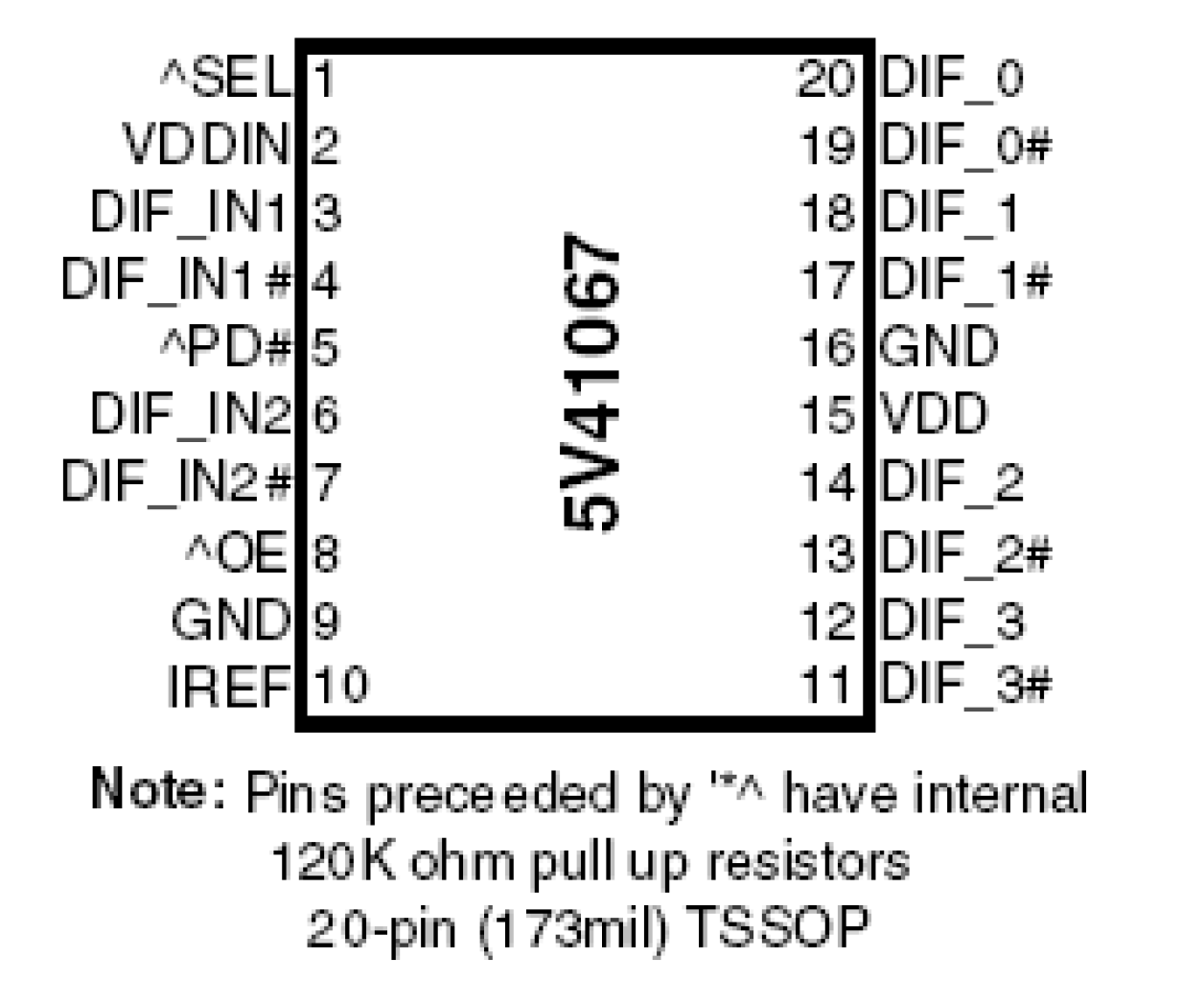

- 20-pin TSSOP package

- small board footprint

- Outputs can be terminated to LVDS

- can drive a wider variety of devices

- OE control pin

- greater system power management

- Industrial temperature range available

- supports demanding embedded applications

- Additive cycle-to-cycle jitter <5 ps

- Additive phase jitter (PCIe Gen2/3) <0.2ps

- Operating frequency up to 200MHz

説明

The 5V41067A is a 2:4 differential clock mux for PCI Express applications. It has very low additive jitter making it suitable for use in PCIe Gen2 and Gen3 systems. The 5V41067A selects between 1 of 2 differential HCSL inputs to fanout to 4 differential HCSL output pairs. The outputs can also be terminated to LVDS.

適用されたフィルター