パッケージ情報

| CADモデル: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PGG28 |

| Lead Count (#): | 28 |

| Pkg. Dimensions (mm): | 9.7 x 4.4 x 1.0 |

| Pitch (mm): | 0.65 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 28 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Input Type | HSTL, LVTTL, LVCMOS, LVPECL |

| Output Skew (ps) | 25 |

| Output Voltage (V) | 2.5V, 1.8V, 1.5V |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Core Voltage (V) | 2.5 |

| Input Freq (MHz) | 250 |

| Inputs (#) | 1 |

| Length (mm) | 9.7 |

| MOQ | 2000 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 250 |

| Output Signaling | LVCMOS |

| Output Type | LVCMOS |

| Outputs (#) | 5 |

| Package Area (mm²) | 42.7 |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 9.7 x 4.4 x 1.0 |

| Pkg. Type | TSSOP |

| Product Category | Clock Buffers & Drivers |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 4.4 |

5T905 に関するリソース

説明

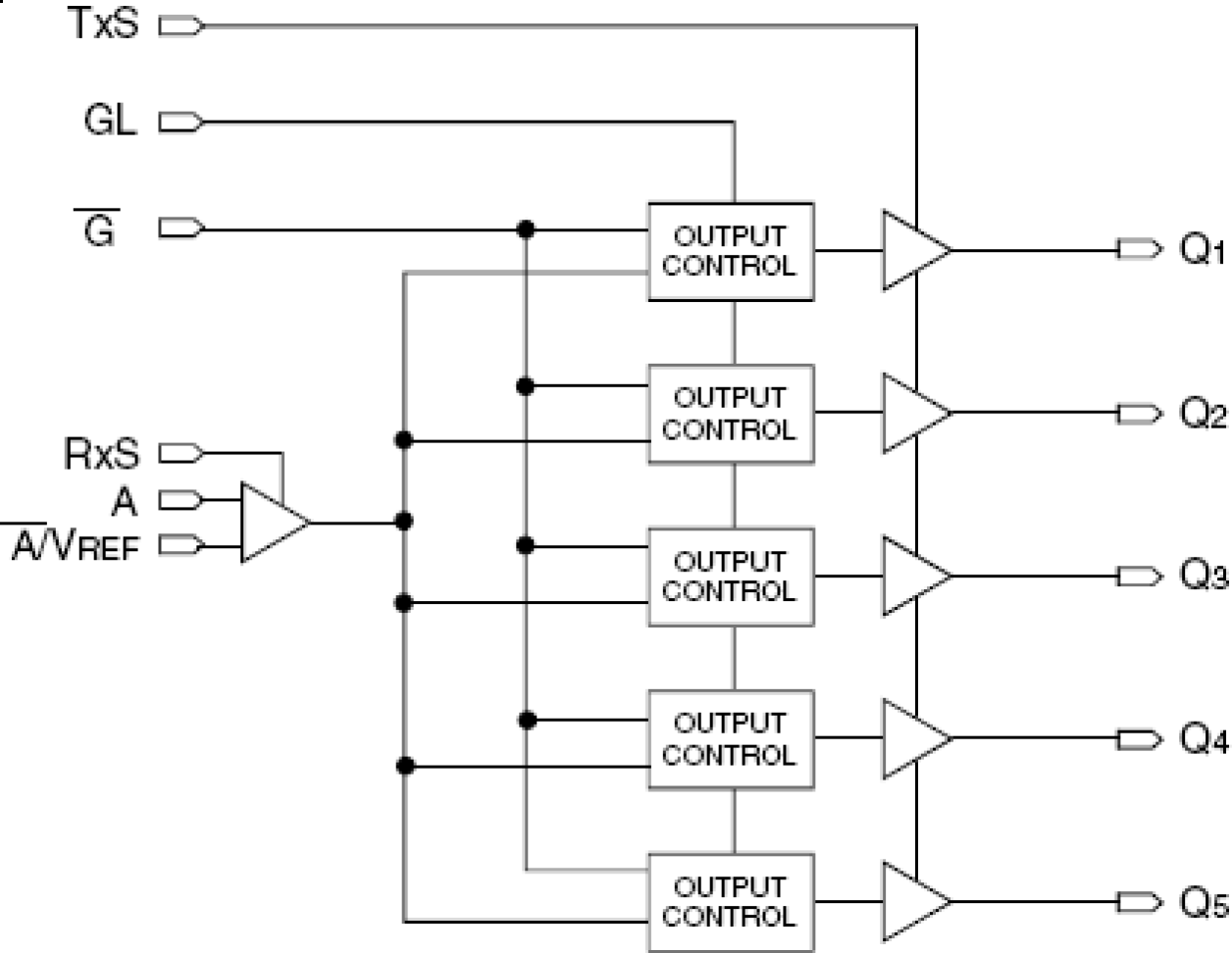

The 5T905 2.5V single data rate (SDR) clock buffer is a user-selectable single-ended or differential input to five single-ended outputs buffer built on advanced metal CMOS technology. The SDR clock buffer fanout from a single or differential input to five single-ended outputs reduces the loading on the preceding driver and provides an efficient clock distribution network. The 5T905 can act as a translator from a differential HSTL, eHSTL, 1.8V/2.5V LVTTL, LVEPECL, or single-ended 1.8V/2.5V LVTTL input to HSTL, eHSTL, 1.8V/2.5V LVTTL outputs. Selectable interface is controlled by 3-level input signals that may be hard-wired to appropriate high-mid-low levels. Multiple power and grounds reduce noise.