パッケージ情報

| CADモデル: | View CAD Model |

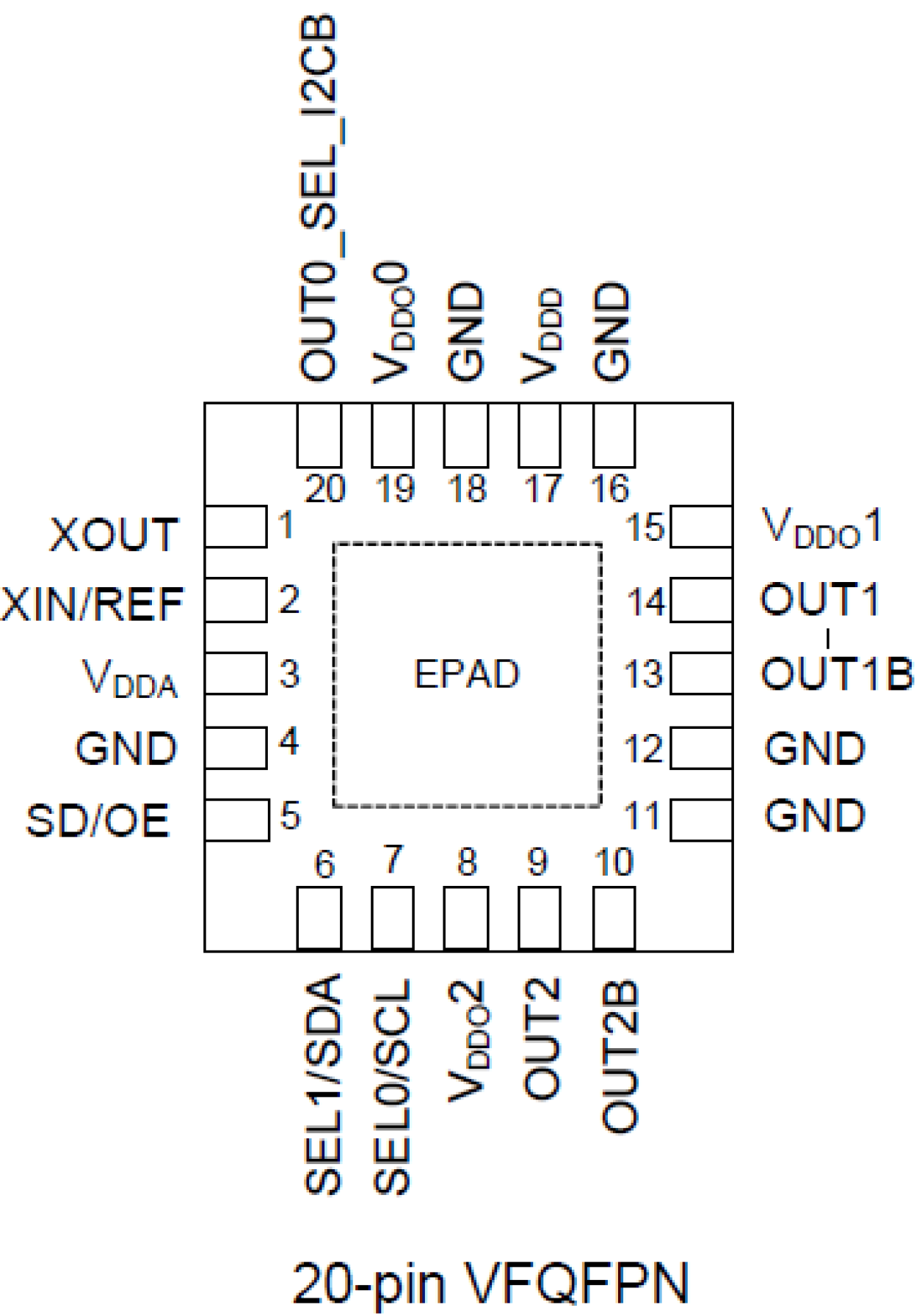

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NDG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 3.0 x 3.0 x 0.9, 3.0 x 3.0 x 1.0 |

| Pitch (mm): | 0.4 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 20 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2500 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Country of Assembly | TAIWAN |

| Country of Wafer Fabrication | SINGAPORE |

| Additive Phase Jitter Typ P-P (fs) | 0.7 |

| Advanced Features | Programmable Clock, Reference Output, Spread Spectrum |

| C-C Jitter Typ P-P (ps) | 46 |

| Core Voltage (V) | 1.8V, 2.5V, 3.3V |

| Family Name | VersaClock 5 |

| Input Freq (MHz) | 1 - 350 |

| Input Type | LVCMOS, Crystal |

| Inputs (#) | 1 |

| Length (mm) | 3 |

| MOQ | 2500 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 1 - 350 |

| Output Skew (ps) | 75 |

| Output Type | LVCMOS, LVPECL, HCSL, LVDS |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Outputs (#) | 3 |

| Package Area (mm²) | 9 |

| Phase Jitter Max RMS (fs) | 1500 |

| Phase Jitter Max RMS (ps) | 1.5 |

| Phase Jitter Typ RMS (fs) | 700 |

| Phase Jitter Typ RMS (ps) | 0.7 |

| Pitch (mm) | 0.4 |

| Pkg. Dimensions (mm) | 3.0 x 3.0 x 1.0 |

| Pkg. Type | VFQFPN |

| Prog. Clock | Yes |

| Prog. Interface | I2C, OTP |

| Reel Size (in) | 13 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 3 |

| Xtal Inputs (#) | 0 |

| 掲載 | No |

5P49V5944 に関するリソース

説明

The 5P49V5944 is a programmable clock generator intended for high-performance consumer, networking, industrial, computing, and data communications applications. Configurations may be stored in on-chip One-Time Programmable (OTP) memory or changed using the I2C interface. This is Renesas' fifth generation of programmable clock technology (VersaClock® 5). The frequencies are generated from a single input reference clock. The input reference can be either a crystal or an LVCMOS reference clock.

Two select pins allow up to four different configurations to be programmed and accessible using processor GPIOs or bootstrapping. The different selections may be used for different operating modes (full function, partial function, and partial power down), regional standards (US, Japan, Europe), or system production margin testing.