パッケージ情報

| Lead Count (#) | 8 |

| Pkg. Code | DCG8 |

| Pitch (mm) | 1.27 |

| Pkg. Type | SOIC |

| Pkg. Dimensions (mm) | 4.9 x 3.9 x 1.5 |

環境及び輸出分類情報

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

製品スペック

| Lead Count (#) | 8 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 97 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range | 0 to 70°C |

| Country of Assembly | Thailand |

| Country of Wafer Fabrication | Singapore |

| Price (USD) | 2.33771 |

| App Jitter Compliance | PCIe Gen1 |

| Architecture | Common |

| C-C Jitter Max P-P (ps) | 80 |

| C-C Jitter Typ P-P (ps) | 65 |

| Core Voltage (V) | 3.3 |

| Diff. Output Signaling | HCSL |

| Diff. Outputs | 1 |

| Diff. Termination Resistors | 4 |

| Input Freq (MHz) | 25 - 25 |

| Input Type | Crystal, LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 4.9 |

| MOQ | 291 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 100 - 100 |

| Output Type | HCSL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 1 |

| PLL | Yes |

| Package Area (mm²) | 19.1 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 4.9 x 3.9 x 1.5 |

| Pkg. Type | SOIC |

| Power Consumption Typ (mW) | 182 |

| Prog. Clock | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | No |

| Thickness (mm) | 1.5 |

| Width (mm) | 3.9 |

| Xtal Freq (MHz) | 25 - 25 |

557-01 に関するリソース

説明

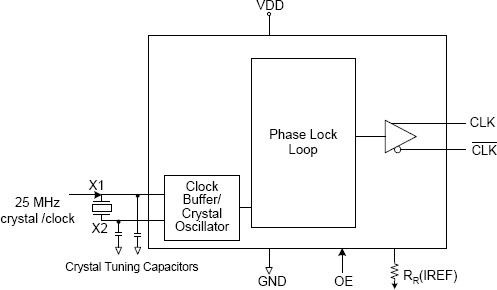

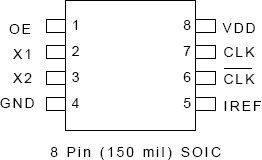

The 557-01 is a clock chip designed for use in PCI Express® cards as a clock source. It provides a pair of differential outputs at 100MHz in a small 8-pin SOIC package. Using Renesas' patented Phase-Locked Loop (PLL) techniques, the device takes a 25MHz crystal input and produces HCSL (Host Clock Signal Level) differential outputs at 100MHz clock frequency. LVDS signal levels can also be supported via an alternative termination scheme.