Features

- Single-ended input reference clock

- Six single-ended clock outputs

- Internal PLL does not require external loop filter components

- 5V tolerant inputs

- Maximum output frequency: 80MHz, (Q0:Q4 outputs)

- Maximum output frequency: 40MHz, (Q/2 output)

- LVCMOS interface levels for all inputs and outputs

- PLL disable feature for low-frequency testing

- Output drive capability: ±24mA

- Output skew: 300ps (maximum), Q0:Q4 and Q/2

- Full 3.3V supply voltage

- Available in lead-free (RoHS 6) package

- -40°C to 85°C ambient operating temperature

- Fully pin and function compatible with the IDTQS5LV931 (including 50, 66 and 80MHz options)

Description

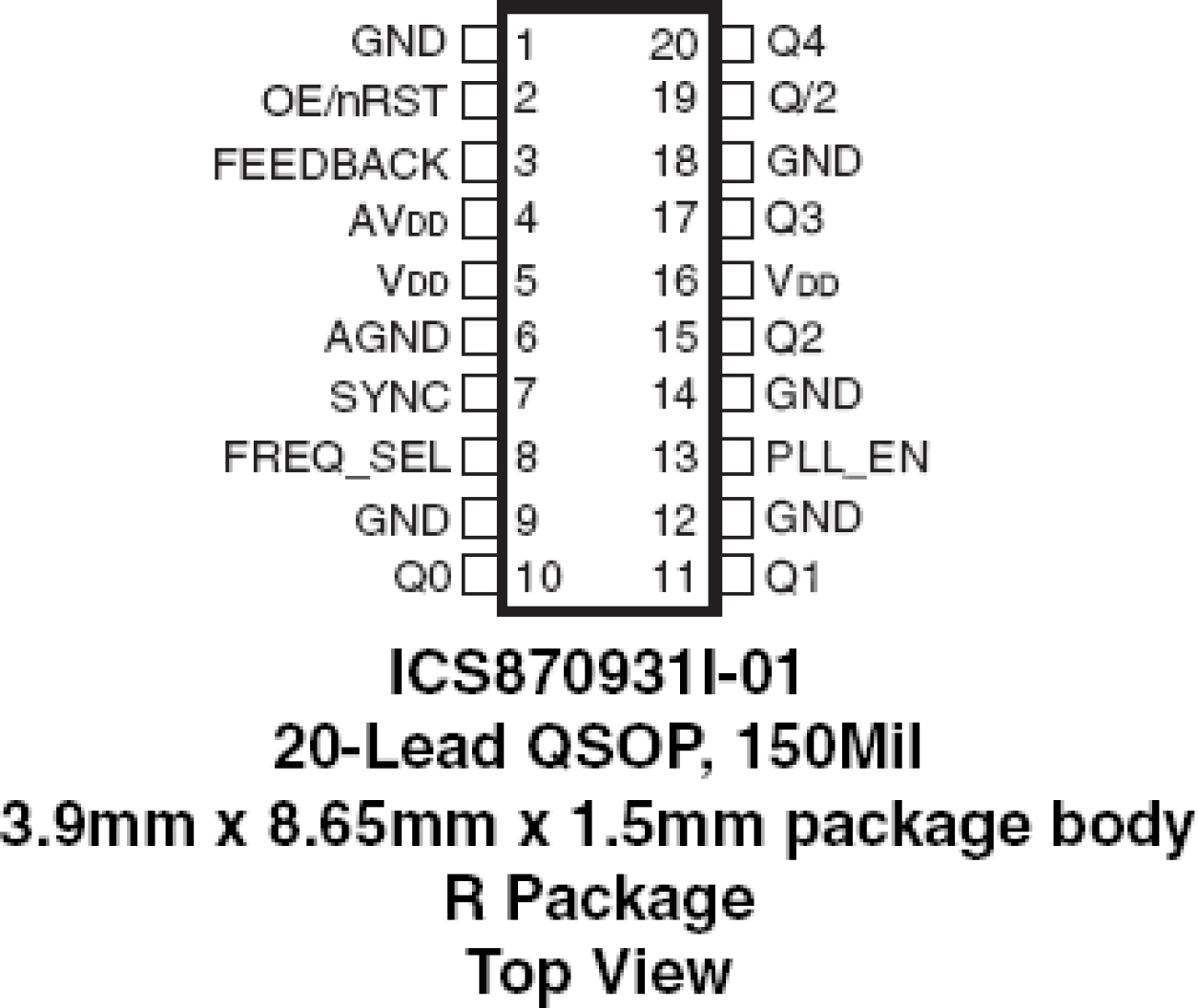

The 870931I-01 is an LVCMOS clock generator that uses an internal phase lock loop (PLL) for frequency multiplication and to lock the low-skew outputs to the reference clock. The device offers six outputs. The PLL loop filter is completely internal and does not require external components. Several combinations of the PLL feedback and a divide-by-2 (controlled by FREQ_SEL) allow applications to optimize frequency generation over a wide range of input reference frequencies. The PLL can also be disabled by the PLL_EN control signal to allow for low frequency or DC testing. The 870931I-01 device is a member of the family of high performance clock solutions from IDT.

Applied Filters: