Features

- Frequency range: 0.016MHz to 1500MHz

- Output Types: LVDS, LVPECL, HCSL, LVCMOS

- Supply Voltage: 1.8V, 2.5V, or 3.3V

- Phase Jitter (12kHz to 20MHz): 300fs typical (400fs max)

- Package options:

- 5.0mm x 3.2mm x 1.2mm

- 7.0mm x 5.0mm x 1.3mm

- Frequency stability: ± 20ppm, ± 25ppm, ± 50ppm, or ± 100ppm

- Operating temperatures: -20 °C to +70 °C

- Frequency stability: ± 25ppm, ± 50ppm, or ± 100ppm

- Operating temperatures: -40 °C to +85 °C

- Frequency stability: ± 50ppm, or ± 100ppm

- Operating temperatures: -40 °C to +105 °C

Description

The XU is a quartz-based PLL clock oscillator family with <400fs phase jitter, supporting a wide range of frequencies, input voltages, and output types. These devices are designed to operate at three different power supplies and are available in multiple package sizes as well as temperature grades.

With a patented one-time program (OTP) allowing for infinite memory shelf life, the XU devices can be programmed to generate an output frequency from 16kHz to 1500MHz with a resolution as low as 1Hz accuracy. The configuration capability of this family of devices allows for fast delivery times for both sample and large production orders.

This device is factory-configurable.

Try the Custom Part Configuration Utility.

Try the Custom Part Configuration Utility.

Parameters

| Attributes | Value |

|---|---|

| Function | XO |

| Output Type | HCMOS, LVDS, LVPECL, HCSL |

| Output Freq Range (MHz) | 0.75 - 1350 |

| Supply Voltage (V) | 3.3 - 3.3, 2.5 - 2.5, 1.8 - 1.8 |

| Phase Jitter Max RMS (ps) | 0.4 |

| Freq. Stability Total (± PPM) | 20, 25, 50, 100 |

| Temp. Range (°C) | -20 to +70, -40 to +85, -40 to +105 |

| Product Category | Crystal Oscillators |

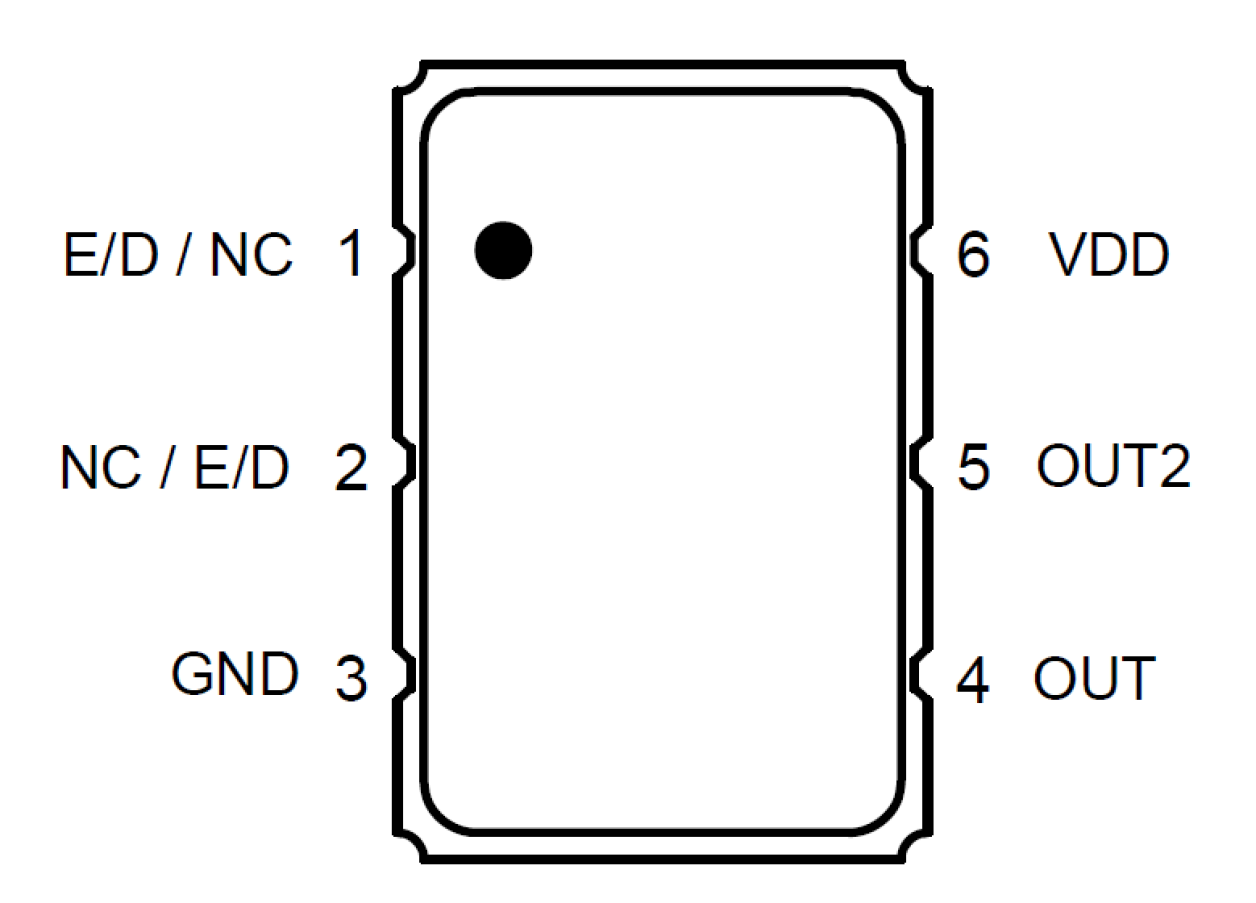

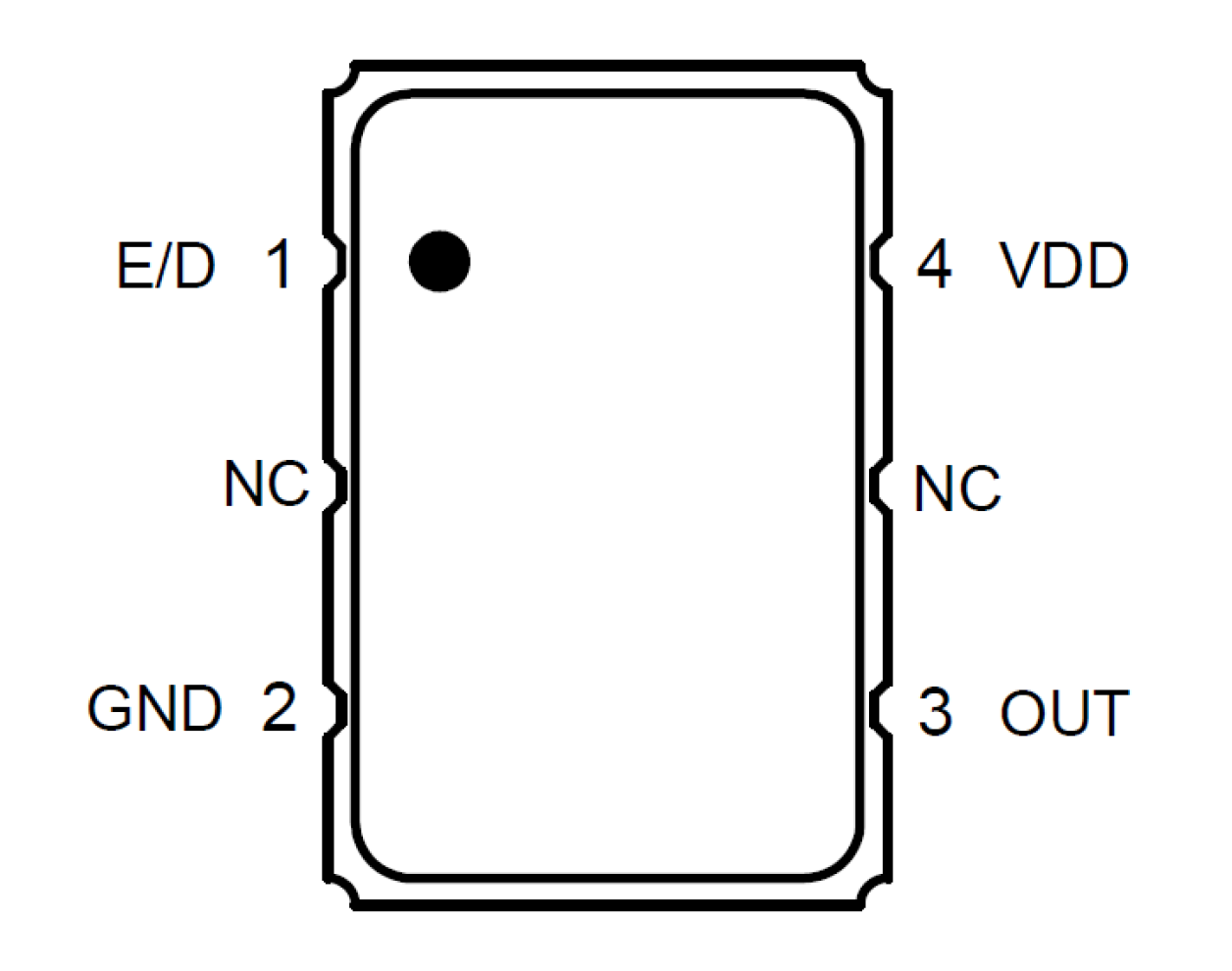

Package Options

| Lead Count (#) |

|---|

| 6 |

Application Block Diagrams

| AMD 4th-Gen EPYC (Genoa) Power & Timing System Complete power and timing system for AMD Genoa with SVI3, DDR5, and PCIe Gen 5/6 support. |

| Power & Timing SoM for RZ/G2E Power and timing SoM ensures precise timing and efficient power distribution. |