H8S Microcomputer with On-Chip IEBus Features

On-Chip IEBus Controller (Implementing IEBus Control with Hardware)

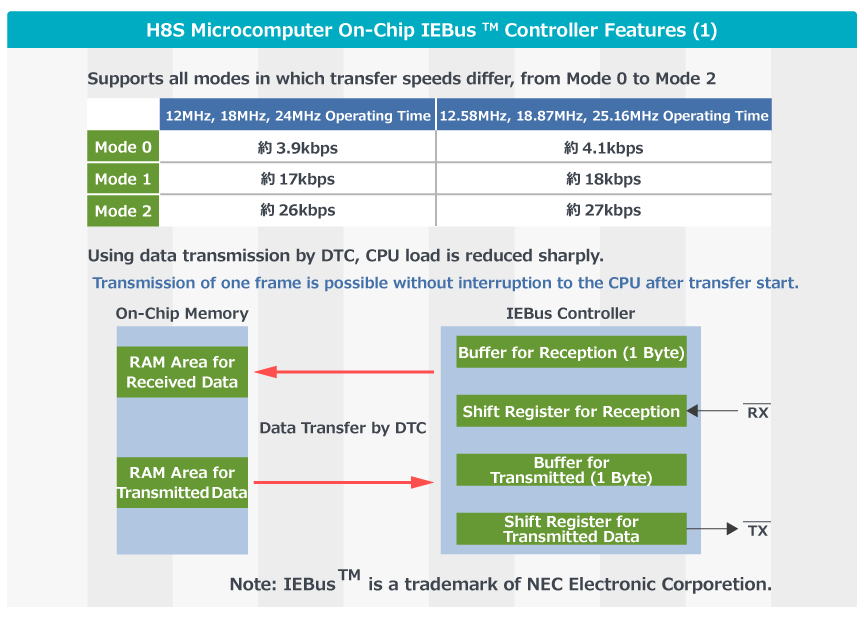

- Supports all modes in which transfer speeds differ, from "Mode 0" to "Mode 2"

- Using data transmission by data transfer controller (DTC), CPU load is reduced sharply (Approx. 1/2)

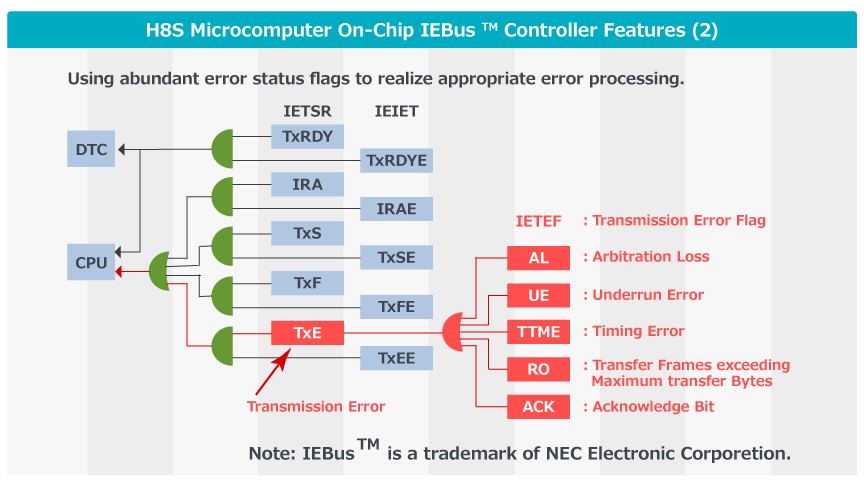

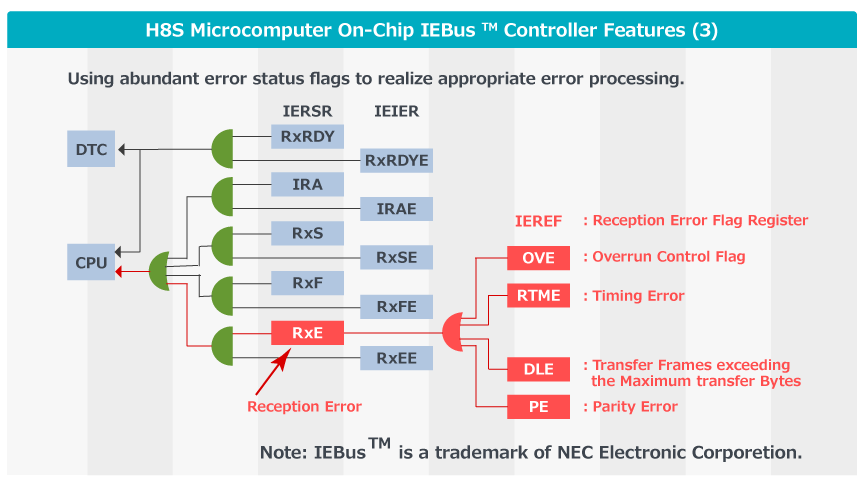

- Uses abundant error status flags to realize appropriate error processing

IEBus Selection by Application

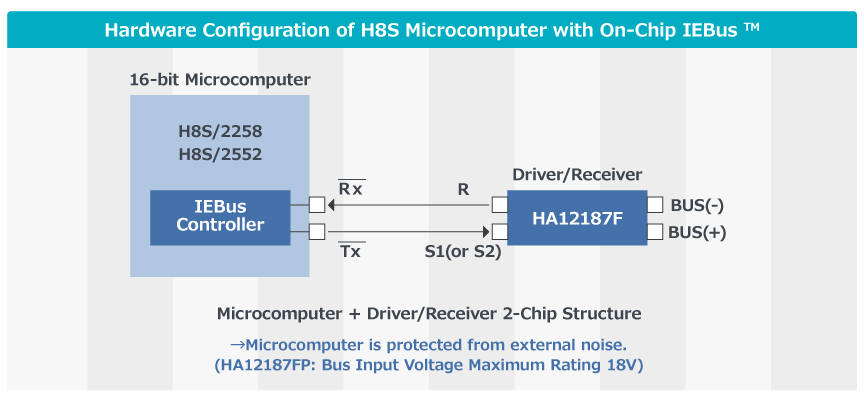

H8S/2258 Group

On-chip peripheral functions required for system configuration include DTC bus masters, ROM and RAM memory, a 16-bit timer-pulse unit (TPU), 8-bit timer (TMR), watchdog timer (WDT), serial communication interface (SCI), I2C bus interface (IIC), IEBus controller (IEB), A/D converter, D/A converter, and I/O ports.

H8S/2556 Group, H8S/2552 Group, H8S/2506 Group

This LSI is a high-performance microcomputer made up of the H8S/2000 CPU with an internal 32-bit configuration as its core, and the peripheral functions required to configure a system.

Support

Support Communities

Get quick technical support online from Renesas Engineering Community technical staff.

Knowledge Base

Browse our knowledge base for helpful articles, FAQs, and other useful resources.