Package Information

| CAD Model: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PKG128 |

| Lead Count (#): | 128 |

| Pkg. Dimensions (mm): | 20.0 x 14.0 x 1.4 |

| Pitch (mm): | 0.5 |

Environmental & Export Classifications

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.32.0041 |

Product Attributes

| Lead Count (#) | 128 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Country of Assembly | TAIWAN |

| Country of Wafer Fabrication | TAIWAN, USA |

| Access Time (ns) | 10 |

| Architecture | Dual-Port |

| Bus Width (bits) | 18 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 2304 |

| Function | Busy, Interrupt, JTAG, Master, Slave |

| I/O Type | 3.3 V LVTTL |

| Interface | Async |

| Length (mm) | 20 |

| MOQ | 24 |

| Organization | 128K x 18 |

| Package Area (mm²) | 280 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 20.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Price (USD) | $234.82833 |

| Qty. per Carrier (#) | 72 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

Resources for 70V639

Description

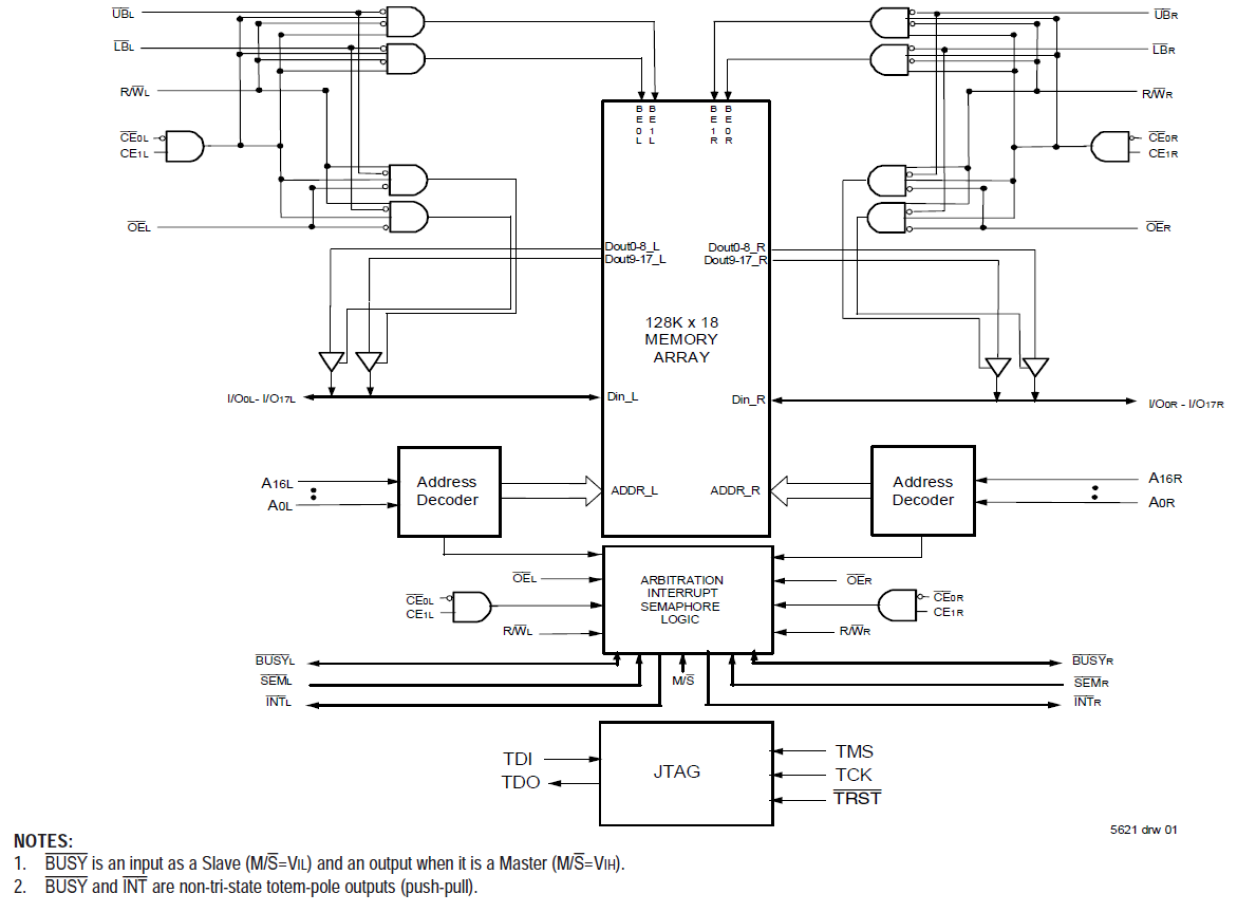

The 70V639 is a high-speed 128K x 18 asynchronous dual-port static RAM designed to be used as a stand-alone dual-port RAM or as a combination Master/Slave dual-port RAM for 36-bit or more word systems. Using the Master/Slave dual-port RAM approach in 36-bit or wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic. An automatic power-down feature controlled by the chip enables (either CE0 or CE1) permits the on-chip circuitry of each port to enter a very low standby power mode.