特長

- 9 HSTL outputs

- Selectable differential CLK, nCLK, or LVPECL clock inputs

- HSTL_CLK, nHSTL_CLK pair can accept the following differential input levels:

LVPECL, LVDS, HSTL, SSTL, HCSL - PECL_CLK, nPECL_CLK supports the following input types:

LVPECL, CML, SSTL - Maximum output frequency: 500MHz

- Output skew: 100ps (maximum)

- Part-to-part skew: 300ps (maximum)

- Propagation delay: 1.7ns (maximum)

- VOH = 1.4V (maximum)

- 3.3V core, 1.6V to 3.6V output supply range

- -40 °C to 85 °C ambient operating temperature

説明

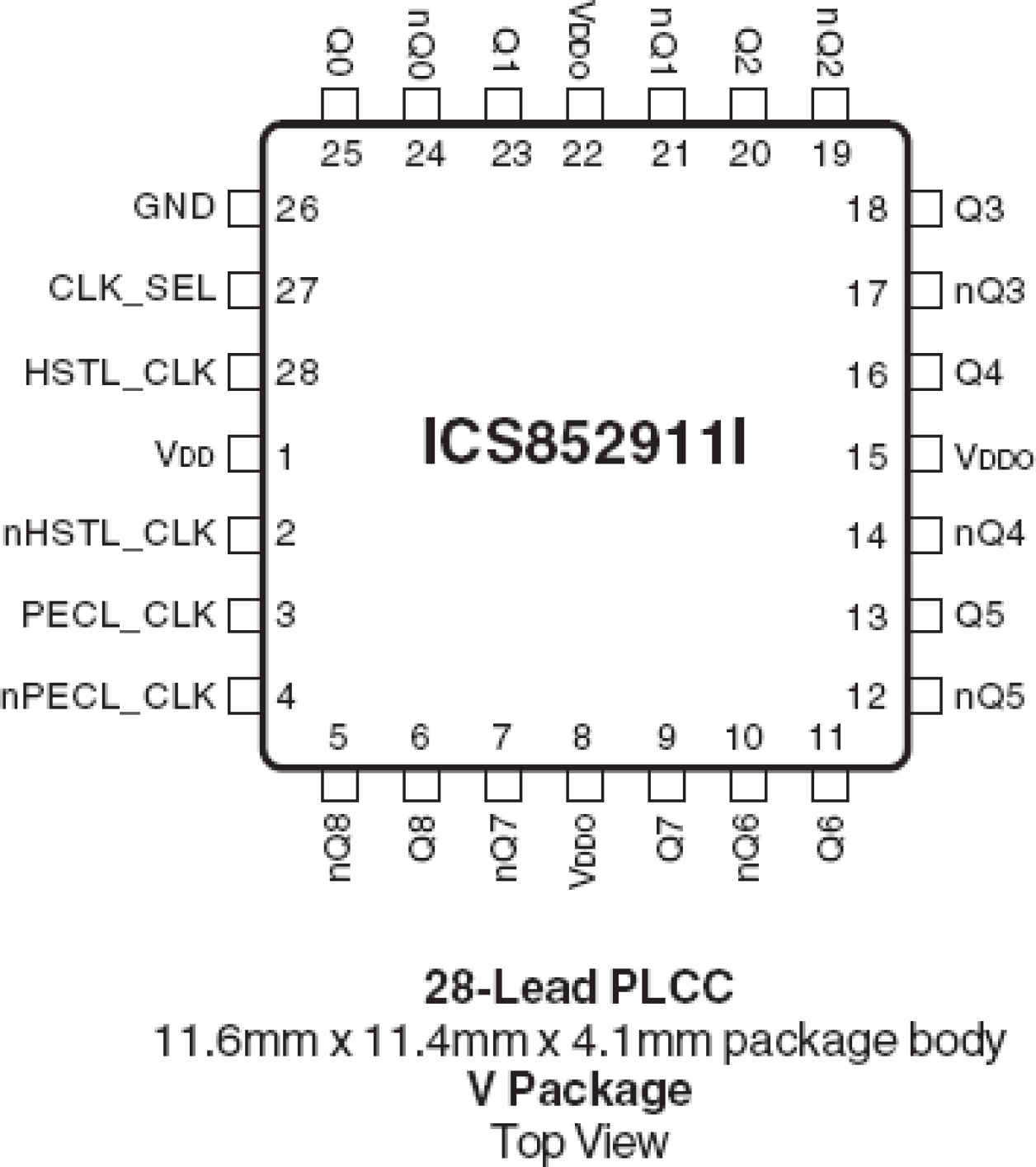

The 852911I is a low-skew, 1-to-9 differential-to-HSTL fanout buffer. The 852911I has two selectable clock inputs which can accept most differential input levels.

Guaranteed output skew, part-to-part skew, and crossover voltage characteristics make the 852911I ideal for today’s most advanced applications, such as IA64 and static RAMs.

適用されたフィルター