ルネサスエレクトロニクス株式会社(代表取締役社長兼CEO:呉 文精、以下ルネサス)は、近年のデータ量の増大に伴いデータセンター内ネットワークで40Gb(ギガビット)から切り替えが進んでいる通信速度2.5倍の100Gbトラフィッククラスのルータ、スイッチ、サーバー等の通信機器向けに、パケットヘッダ検索リファレンスデザインを本日より提供開始します。これは、すでに発売している低消費電力のLow Latencyメモリ(以下、LLDRAM)「LLDRAM-III(RMHE41A364AGBG)」を使用し、新たに開発したFPGA(注1)向け完全一致検索IPと、LLDRAM-IIIコントロールIP、および開発サポートツールを提供するものです。100ギガ世代のパケットヘッダ検索機能を、汎用DRAMメモリで構成した場合に比べて、メモリデバイス数を1/15に、メモリの消費電力を60%削減可能です。

本リファレンスデザインの特長としては、(1)100Gbトラフィックで100万エントリー(注2)以上のパケットヘッダ検索を40Gbトラフィック相当の電力、2Wで実現します。これは、メモリにDRAMを使用した場合と比べてメモリデバイス数を1/15に、メモリの消費電力を60%削減できます。また、(2)検索キー長(注3)を任意に設定できる機能を搭載しており、新たな通信プロトコルにも検索IPの設計変更が不要です。さらに、(3)検証済みのリファレンスデザインを提供するため、ネットワーク機器設計の開発期間を約6か月短縮可能です。

近年、IoT時代の到来とともにネットワークに繋がるモノと流通するデータ量が急増しているため、ネットワークの高速化が進展しています。特にデータセンター内のトラフィックスピードは40Gbから100Gbへの切り替えが進んでおり、検索エントリー数も増加傾向にあります。一方で、ネットワーク機器の高速化に伴う消費電力の増加が、パッケージの熱や電力コストの問題を引き起こします。また、SDN/NFVの普及により、ソフトウェアからネットワーク構成を頻繁に変更するため、フレキシブルに設定変更ができるネットワーク機器が要求されます。このような状況に対し、ルネサスではフレキシブルなネットワークを構成できるFPGAと、100万以上の検索エントリーを格納できるLLDRAM-IIIを利用した高速にトラフィックを処理できる低消費電力のパケットヘッダ検索リファレンスデザインを開発しました。

パケットヘッダ検索リファレンスデザインの特長詳細は以下のとおりです。

(1)100Gbトラフィッククラスで100万エントリー以上のパケットヘッダ検索を40Gb相当の電力、2Wで実現

「LLDRAM-III」は1秒間に400M(メガ)アクセス(書き込み/読み込み)、57.6Gb(ギガビット)転送を2W以下で動作することができる低消費電力が特徴の当社製Low-Latencyメモリ。このメモリと新たに開発した当社の検索アルゴリズムを組み合わせることにより、100Gbトラフィッククラスで要求される1秒間に1億5千万回のパケットヘッダ検索処理を1個のLLDRAM-IIIで実現可能。同等の処理を一般的な検索アルゴリズム(注4)と汎用DRAMで構成した場合、15個程度のメモリが必要となり、消費電力は5W程度になると想定されるため(当社試算)、メモリデバイス数1/15、メモリ消費電力60%減が可能。これにより、メモリ実装面積が9割削減され、さらにメモリとFPGA間の配線数が9割減少することにより、ピン数の少ないFPGAでシステムを構成できるようになるため、コスト低減にも貢献。

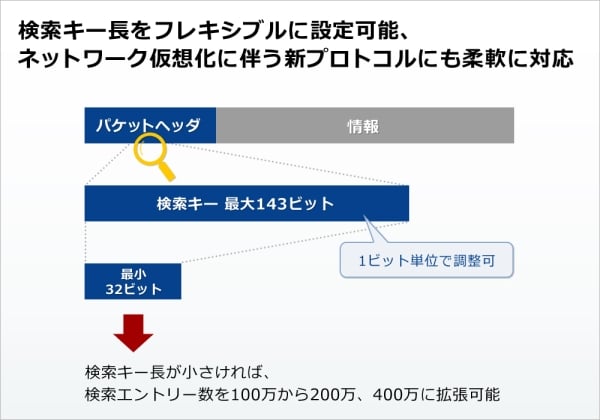

(2)検索キー長を任意設定できる機能を搭載しており、新たな通信プロトコルにも検索IPの設計変更不要で対応可能

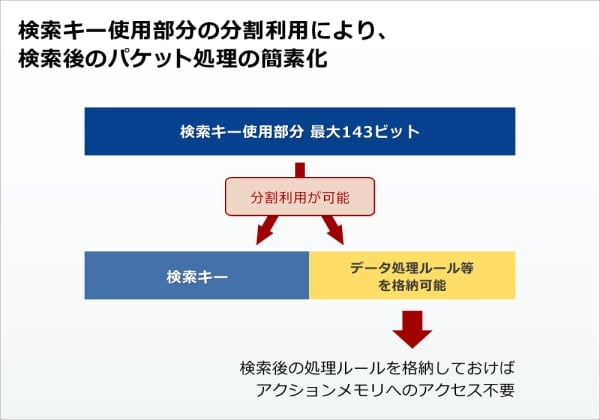

今回新たに開発した完全一致検索IPは、検索キー長を最大143ビット(注5)まで、1ビット単位で任意に変更できる機能を搭載。これにより、従来のMACアドレス検索だけでなく、ネットワーク仮想化技術の進化による新たな通信プロトコルにも検索IPを設計変更することなく対応可能。また、最大検索キーを短く設定することで、検索エントリー数をさらに200万、400万へと拡張することも可能。さらに、検索キーで使用する最大143ビットのビット幅を、検索キーの領域と検索結果に付随するパケット処理ルール領域に分割し、検索結果とパケット処理ルールを同時出力する機能も内蔵。

(3)検証済みのリファレンスデザインによりネットワーク機器設計の開発期間を6か月短縮

開発サポートツールとして、1)設計・検証に時間がかかるFPGAとLLDRAM-III間のインターオペラビリティ(相互運用性)を検証済みのリファレンスボード、2)検証済みの検索IPを含むサンプルデザイン、3)検証環境一式、4)評価環境一式を提供。これにより、ユーザは開発するネットワーク機器のハードウェアの設計と並行してFPGA内のシステム設計・検証をスタートさせることが可能。これにより、6か月程度(当社試算)のシステム開発期間短縮に貢献。

ルネサスではデータセンター外部通信インターフェースや基幹通信網で使用される200Gb以上の複雑な通信処理に向けてはNSE(https://www.renesas.com/ja/about/press-center/news/2015/news20150427.html)を、データセンター内部で使用されるポート数が多い100Gb以下の通信処理には、LLDRAM-IIIと FPGAで構成したパケットヘッダ検索リファレンスデザインを提供いたします。急速に発展しているネットワーク技術の進化に、フレキシブルな通信を可能にするFPGAベースの検索ソリューションを提供することによりICTの発展に貢献していきます。

パケットヘッダ検索リファレンスデザインの製品情報は、https://www.renesas.com/ja/solutions/network-infrastructure/data-center/packet-header-search-solution.html をご覧ください。

以 上

(注1)本リファレンスデザインのFPGAは、ザイリンクス社のVirtex UltraScale / Kintex UltraScale FPGAを利用

(注2)検索エントリーとは、パケットを識別するための検索キー(注3)とパケット転送の宛先で構成される情報

(注3)検索キーとは、パケットを識別するための特定のビット幅を持ったデータ

(注4)TreeBitMapでMACアドレス(48ビット)検索を実施した場合

(注5)143ビットは1Mエントリー設定の場合のみです。2Mエントリーの場合は71ビット、4Mエントリーの場合は35ビットとなります。

*本リリース中の製品名やサービス名は全てそれぞれの所有者に属する商標または登録商標です。

ニュースリリースに掲載されている情報(製品価格、仕様等を含む)は、発表日現在の情報です。 その後予告なしに変更されることがございますので、あらかじめご承知ください。